# An In-Situ Microcoaxial Fabrication and Attachment Strategy

Submitted By Daniela Alejandra Torres

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

#### MASTERS OF SCIENCE IN MECHANICAL ENGINEERING

School of Engineering Tufts University Medford, Massachusetts

May 2018

| Signature of Author:                 | Committee:                           |

|--------------------------------------|--------------------------------------|

| Daniela Alejandra Torres             | Dr. Robert David White               |

| ·                                    | Department of Mechanical Engineering |

|                                      | Tufts University                     |

|                                      |                                      |

|                                      |                                      |

|                                      |                                      |

|                                      |                                      |

| Committee:                           | Committee:                           |

| Dr. Caprice Gray                     | Dr. Marc Hodes                       |

| Department of Mechanical Engineering | Department of Mechanical Engineering |

| Tufts University                     | Tufts University                     |

#### **Abstract**

Micro-coaxial cables (MCCs), with an outer diameter of 100  $\mu$ m or less, enable a new microelectronics packaging platform that will reduce the time required to design and fabricate complex multi-chip microelectronic assemblies. Low-inductance MCCs for power distribution and 30-75  $\Omega$  MCCs for signal distribution, eliminate the need for lengthy simulations and fabrication processes, as in board design of photo-lithographically patterned microchips, because each individually shielded MCC provides sufficient isolation to prevent electro-magnetic interference (EMI) and crosstalk. The in-situ fabrication method presented here utilizes only conventional wire bonding and microfabrication techniques, providing a high-feasibility path toward a new interconnect paradigm based on MCCs.

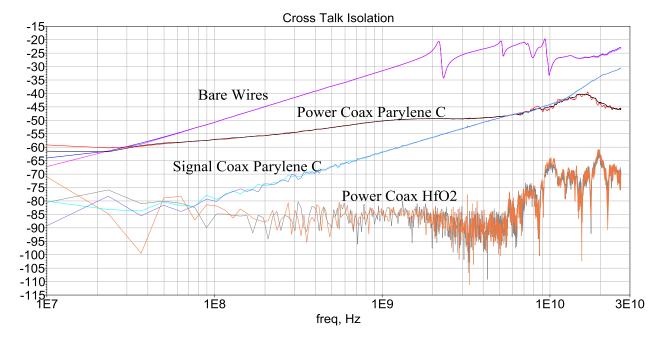

Each cable measured consists of a 25.4  $\mu$ m gold bond wire coated first with a dielectric and then a 5.0  $\mu$ m thick gold shield. For power distribution, the dielectrics evaluated are 1.0  $\mu$ m thick Parylene C dielectric and 100 nm thick HfO<sub>2</sub>. Their characteristic impedances are measured to be 3.2-5.9  $\Omega$  and 0.11-0.18  $\Omega$ , respectively. A third MCC, appropriate for signals, has a 38  $\mu$ m thick Parylene C dielectric and a characteristic impedance of 39-68  $\Omega$ . For a wire pitch of 0.51 mm cross-talk is -62 dB at 1 GHz for micro-coax. Cross-talk increases to -30 dB at 26.5 GHz.

#### Acknowledgements

I would like to thank my adviser, Professor Robert White, who has, since I was an undergraduate at Tufts University, supported, advised, and extended his expertise throughout my academic career. His guidance has had a significant impact on my technical skills, interests, and academic performance. Without him I would not be the student, engineer, or person I am today. I would also like to thank my Draper adviser, Caprice Gray, who has made the transition from Tufts to Draper a wonderful experience. Her insights and instructions particularly on the Miniature Multi-Wire Systems project and Draper has been invaluable. I am also very grateful for the generous financial support by her project and the Draper Fellows program. I would also like to thank my third thesis adviser, Professor Marc Hodes, who has been supportive throughout my graduate experience particularly in reviewing my thesis work and dissertation and providing useful feedback.

I am grateful for the generous technical support given to me by Draper staff and Draper Technicians. I would like to thank Tony Kopa who has taught me everything I now know about RF microelectronics, for training me on equipment and modeling software, as well as advising me throughout the project whether it be through presentations, results, or publications. Similarly, I would like to thank Sara Barron and Bob McCormick who have assisted me in microfabrication as well as assisted me throughout the publication process. Additionally, I would like to thank Yen Wah for all her wire bonding help, Prasit Sricharoenchaikit for his electroplating help, Mark Singleton for assisting me with laser etching, and Peter Lewis for his help with the FIB. Finally, I'd like to thank everyone else on the Miniature Multi-Wire Systems team as well as Brian Smith who has served as an

additional adviser at Draper during my time as a fellow. I am also grateful for the support of the Mechanical Engineering Department as well as the staff at the Tufts Micro and Nano Fabrication Lab. I particularly would like to thank Jim Vlahakis who has supported my clean room work since I was an undergraduate student.

Finally, I'd like to thank all my fellow graduate school friends for all the good memories that we've had together. I wish them all the best of luck in their studies. I'd like to give a special thank you to Kevin Ligonde who has been my engineer partner in crime since day one of our studies. I'd also like to thank my family and my boyfriend, Matthew, who have been supporting me since my freshman year at Tufts. I am forever grateful for all the love and support from everyone that has been a part of this experience.

## **Table of Contents**

| 1 | Intr   | roduction and Background                                                       | 1  |

|---|--------|--------------------------------------------------------------------------------|----|

|   | 1.1    | System on Chip (SoC) vs. System in Package (SiP)                               | 1  |

|   | 1.1    | .1 SiP Market                                                                  | 3  |

|   | 1.2    | Radio Frequency Waves and Microwaves                                           | 3  |

|   | 1.3    | Micro-Coaxial Interconnects for SiP RF Modules                                 |    |

|   | 1.3    | .1 Nuvotronics Coaxial Waveguide and Reconfigurable RF Components              | 6  |

|   | 1.3    |                                                                                |    |

|   | 1.3    | .3 In-Situ Fabrication and Attachment of Micro-Coax                            | 8  |

|   | 1.3    | .4 Miniature Multi-Wire Systems                                                | 9  |

|   | 1.4    | •                                                                              |    |

| 2 | Bac    | ckground Theory                                                                | 13 |

|   | 2.1    | Transmission Line Basics                                                       | 13 |

|   | 2.2    | Transmission Line Parameters for Coaxial Cables                                | 15 |

|   | 2.3    | Two-Port Network Theory and Scattering (s) Parameters                          | 18 |

|   | 2.4    | Four-Port Network Theory                                                       |    |

|   | 2.5    | De-embedding                                                                   | 21 |

|   | 2.6    | Plotting and Interpretation of S-Parameters                                    | 23 |

|   | 2.6    | .1 Smith Chart                                                                 |    |

|   | 2.6    | .2 Magnitude vs. Frequency Plot                                                | 26 |

| 3 | Cha    | aracterization of Low Impedance Micro-Coaxial Cables for Power Distribution    | 28 |

|   | 3.1    | Abstract                                                                       | 28 |

|   | 3.2    | Introduction                                                                   | 28 |

|   | 3.3    | Low Impedance Microcoax Design                                                 | 30 |

|   | 3.3    | .1 Case Studies of a Power Distribution Network                                | 31 |

|   | 3.3    | .2 Resistance, Inductance, Characteristic Impedance and Capacitance of         |    |

|   | Coa    | axial Cables                                                                   | 35 |

|   | 3.4    | Low Inductance Microcoax Fabrication                                           |    |

|   | 3.5    | Two-Port RF Characterization                                                   | 43 |

|   | 3.5    | · · · · · · · · · · · · · · · · · · ·                                          |    |

|   | 3.5    | .2 Circuit Modeling in Advanced Design System (ADS)                            | 44 |

|   | 3.6    | Results                                                                        | 45 |

|   | 3.7    | Conclusions and Future Work                                                    |    |

| 4 | Co-    | -fabrication of Micro-Coaxial Interconnects and Substrate Junctions for Multi- |    |

| C | hip Mi | croelectronic Systems                                                          | 48 |

|   | 4.1    | Introduction                                                                   |    |

|   | 4.2    | In-Situ Microcoax Fabrication and Attachment                                   | 49 |

|   | 4.3    | Microcoaxial Fabrication and Analytical Calculations of Capacitance,           |    |

|   | Induc  | tance, and Characteristic Impedance                                            | 52 |

|   | 4.3    | .1 Low Inductance Microcoax with HfO <sub>2</sub> Dielectric                   | 52 |

|   | 4.3    | · · · · · · · · · · · · · · · · · · ·                                          |    |

|   | 4.3    | 5                                                                              | 55 |

|   | 4.3    | .4 Analytical Derivations for Capacitance, Inductance, and Characteristic      |    |

|   | Im     | pedance for Fabricated Microcoax                                               | 56 |

|   | 4.4     | Extraction of Electrical Properties of Microcoax With 2-Port RF Network      |    |

|---|---------|------------------------------------------------------------------------------|----|

|   | Analy   | sis                                                                          | 58 |

|   | 4.4     |                                                                              |    |

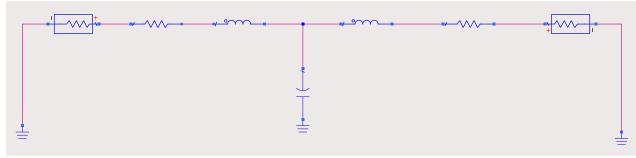

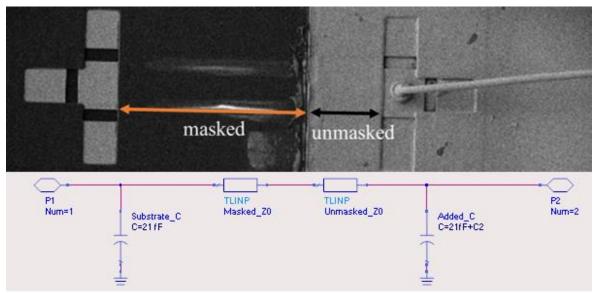

|   | 4.4     | 2 ADS Circuit Simulations                                                    | 60 |

|   | 4.5     | Measured S-Parameter Results                                                 | 63 |

|   | 4.5     | 1 Electrical Results for Low Inductance HfO <sub>2</sub> Microcoax           | 63 |

|   | 4.5     | 2 Electrical Results for Low Inductance Parylene Microcoax                   | 65 |

|   | 4.5     | 3 Electrical Results for Signal Parylene Microcoax                           | 67 |

|   | 4.5     | 4 Summary of Electrical Results                                              | 69 |

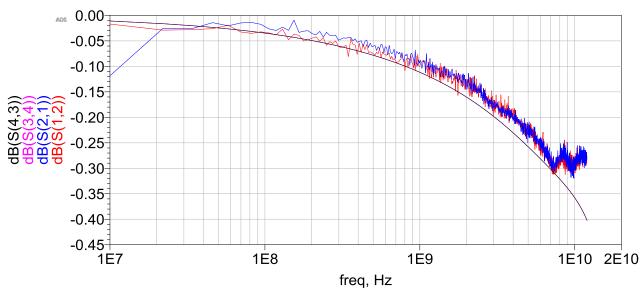

|   | 4.6     | Cross-Talk Measurements and Results                                          | 71 |

|   | 4.6     | 1 Cross-Talk Results                                                         | 71 |

|   | 4.7     | Conclusions                                                                  | 73 |

|   | 4.8     | Future Work                                                                  | 75 |

| 5 | Coı     | nclusions and Future Work                                                    | 76 |

|   | 5.1     | PDN                                                                          |    |

|   | 5.2     | Inductance and Resistance                                                    | 76 |

|   | 5.3     | Microcoax Fabrication                                                        | 77 |

|   | 5.4     | De-Embedding                                                                 |    |

|   | 5.5     | VNA                                                                          |    |

|   | 5.6     | ADS Modeling                                                                 |    |

|   | 5.7     | Transmission Line Theory                                                     |    |

| A |         | X                                                                            |    |

|   |         | DS Transmission Line Model Fit Parameters                                    |    |

|   |         | requency dependence of R and L                                               |    |

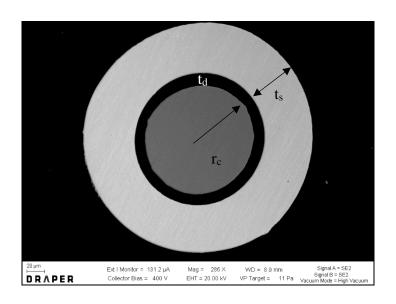

|   |         | IB with 25.4 μm diameter core, 3.0 μm Parylene C dielectric, Evaporated Ti/O |    |

|   |         | n/150nm) Seed Layer, and 5.0 μm of Au plated metal.                          |    |

|   |         | ariation in Au plating Quality on Different RF Boards                        |    |

|   |         | ser Etching of Thick Dielectric to Access GSG Probe Locations                |    |

| R | eferend | es                                                                           | 87 |

## **Table of Figures**

| Figure 1-1 Packaging hierarchy using PCB technology                                                        | 1  |

|------------------------------------------------------------------------------------------------------------|----|

| Figure 1-2 3D Packaging Techniques                                                                         |    |

| Figure 1-3 Break down of SiP market demands                                                                | 3  |

| Figure 1-4 Frequency spectrum of RF waves and Microwaves                                                   | 4  |

| Figure 1-5 Images of a coaxial waveguide microstructure                                                    | 6  |

| Figure 1-6 Schematic of a fully integrated RF module by Nuvotronics                                        |    |

| Figure 1-7 a. Routed connections using Multi-Wire Board technology                                         |    |

| Figure 1-8 Outline of Signal Micro-Coax Fabrication                                                        |    |

| Figure 1-9 Illustration of MMS technology                                                                  |    |

| Figure 2-1 Basic Transmission Line Representation                                                          |    |

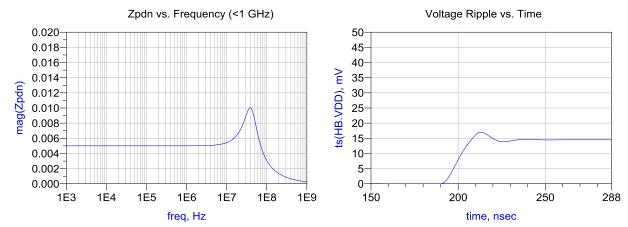

| Figure 2-2 Scanning Electron Microscope image of fabricated micro-coax.                                    |    |

| Figure 2-3 Schematic of a two-port network.                                                                |    |

| Figure 2-4 Two-Port Network                                                                                |    |

| Figure 2-5 Signal flow graph of a two-port network analysis of a DUT                                       |    |

| Figure 2-6 Overview of a Smith Chart                                                                       | 24 |

| Figure 2-7 Ideal capacitor behavior with minimal inductance                                                |    |

| Figure 2-8 Behavior of transmission coefficients                                                           |    |

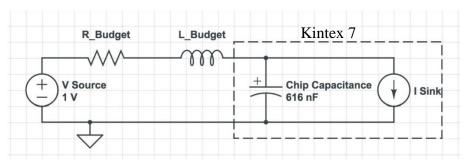

| Figure 3-1 PDN Used to Estimate R <sub>budget</sub> and L <sub>budget</sub> for the Kintex 7 FPGA          |    |

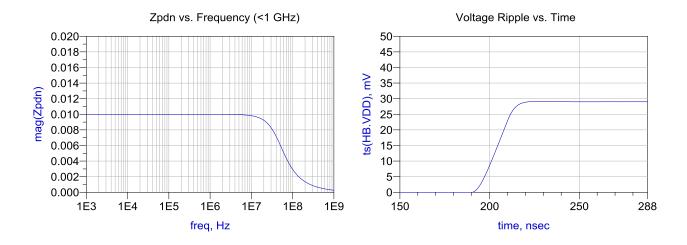

| Figure 3-2 Frequency of Zpdn Case 1                                                                        |    |

| Figure 3-3 Frequency of Zpdn Case 2                                                                        |    |

| Figure 3-4 Scanning Electron Microscope cross section of fabricated microcoax                              |    |

| Figure 3-5 Inductance per unit length in H/m versus dielectric thickness                                   |    |

| Figure 3-6 Resistance per unit length in H/m versus shield thickness                                       |    |

| Figure 3-7 Fabrication steps for developing stripped microcoaxial cables.                                  |    |

| Figure 3-8 SEM image of micro-coax after fabrication process.                                              |    |

| Figure 3-9 Schematic of 2-port RF test fixture                                                             |    |

| Figure 3-10 Discrete Model of Micro-Coax                                                                   |    |

| Figure 3-11 Cell Model of Micro-Coax Segment                                                               |    |

| Figure 4-1 Micro-Coax Fabrication                                                                          |    |

| Figure 4-2 FIB cross section of micro-coax with 100 nm HfO <sub>2</sub>                                    |    |

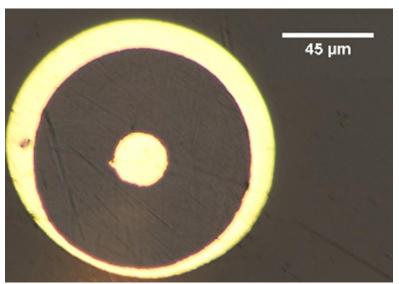

| Figure 4-3 FIB cross section of micro-coax with 21.0 µm parylene C                                         |    |

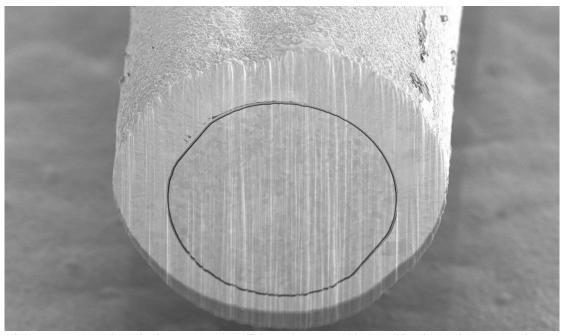

| Figure 4-4 Potted cross section of micro-coax with 38.0 µm parylene C                                      |    |

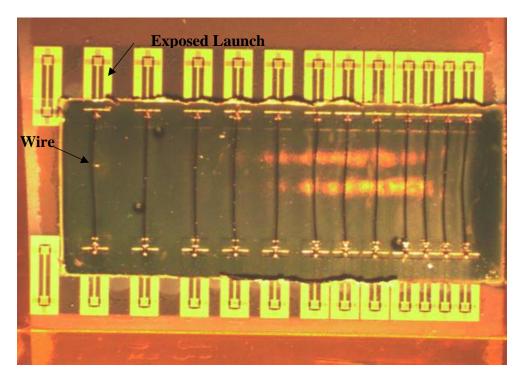

| Figure 4-5 Illustration of one pair of launches                                                            |    |

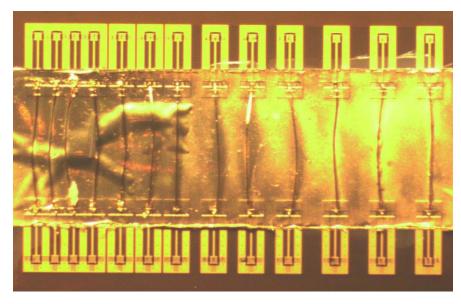

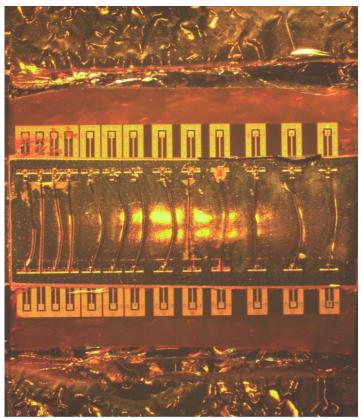

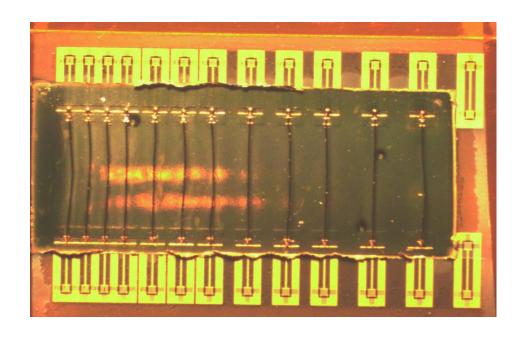

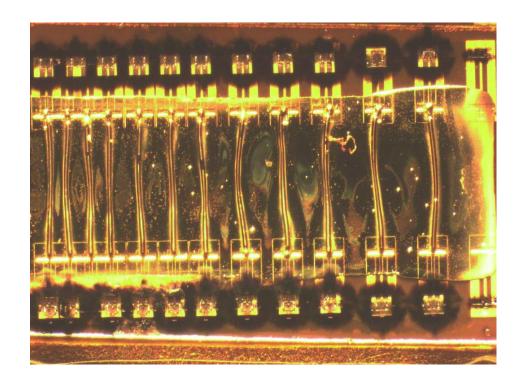

| Figure 4-6 Microscope image of RF board with 12 microcoaxial cables                                        |    |

| Figure 4-7 ADS circuit model of microcoax                                                                  |    |

| Figure 4-8 ADS transmission line model                                                                     | 61 |

| Figure 4-9 Substrate model of RF board                                                                     |    |

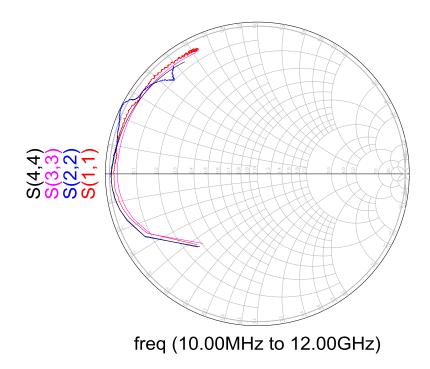

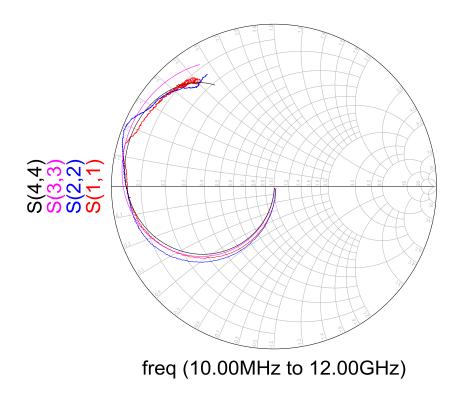

| Figure 4-10 Reflection s-parameters from 10 MHz to 12 GHz HfO2                                             |    |

| Figure 4-11 Transmission s-parameters from 10 MHz to 12 GHz HfO2                                           |    |

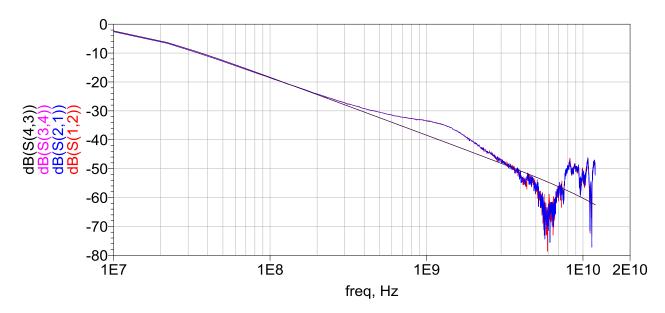

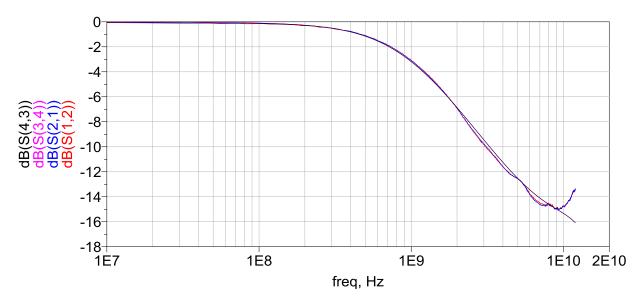

| Figure 4-12 Reflection s-parameters from 10 MHz to 12 GHz paylene C                                        |    |

| Figure 4-13 Transmission s-parameters from 10 MHz to 12 GHz parylene C                                     |    |

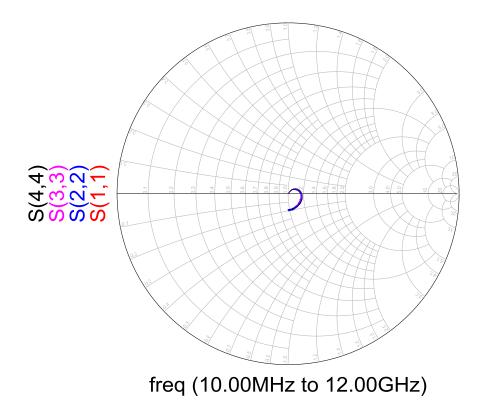

| Figure 4-14 Reflection s-parameters from 10 MHz to 12 GHz parylene C signal                                |    |

| Figure 4-15 Transmission s-parameters from 10 MHz to 12 GHz parylene C signal                              |    |

| Figure 4-16 Bare Au wires with a 25.4 µm diameter bonded onto GSG pads                                     |    |

| Figure 4-17 Magnitude of S <sub>14</sub> and S <sub>23</sub> in dB plotted versus frequency up to 26.5 GHz | 13 |

## **Table of Tables**

| Table 1-1 Summary of Coaxial Transmission Lines for SiP and Their Properties | 10 |

|------------------------------------------------------------------------------|----|

| Table 3-1 Important Properties of Coax That Influence Electrical Properties  | 36 |

| Table 3-2 Summary of Target Microcoaxial Geometry for Fabrication            | 40 |

| Table 3-3 Analytical, Measured, and Simulated Electrical Properties          | 46 |

| Table 4-1 Expected L, C, and Z <sub>0</sub> From Fabrication                 | 58 |

| Table 4-2 L, C, and Z0 for Power Coax with 100 nm Thick HfO <sub>2</sub>     |    |

| Table 4-3 L, C, and Z0 for Power Coax with 1.0 µm Thick Parylene C           |    |

| Table 4-4 Z <sub>0</sub> for Signal Coax with 38 μm Thick Parylene C         |    |

## 1 Introduction and Background

#### 1.1 System on Chip (SoC) vs. System in Package (SiP)

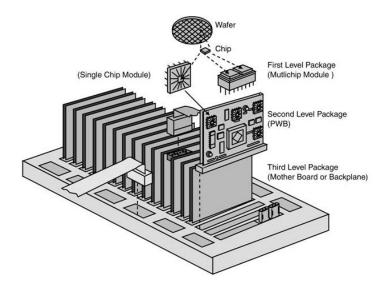

A common architecture in packaging electronics is a 2D assembly of single chip modules, or multichip modules, on a printed circuit board (PCB) [1]. This arrangement allows for a packaging hierarchy where PCBs may be integrated with other PCBs or external hardware via a motherboard or backplane [2]. An image of a typical assembly using PCBs can be seen in Figure 1-1. This packaging scheme has allowed designers to focus on fabricating integrated circuits (ICs) on chips. The fabrication of complex circuits on a die is also referred to as System on Chip (SoC) [3].

Figure 1-1 Packaging hierarchy using PCB technology. Image taken from [2].

SoC has reached some of its limitations in fabrication. As the need for miniaturization and more functionality on a chip increases, fabrication becomes more difficult to implement [3]. There are continuing demands for further miniaturization, complex power distribution, cost reduction, customization, and quick turnaround time for packaging technology. Devices such as smartphones, pacemakers, automotive systems, and other devices, parts of the "Internet of Things (IoT)" are

demanding more heterogeneous technology integration [4]. As a result, designers have begun to focus their attention to making complex systems at the package level by assembling two or more dissimilar chips into a package. This advanced packaging platform is known as the System in Package (SiP) [4].

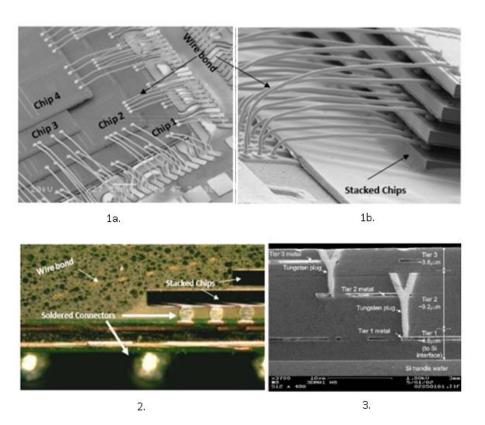

SiP may incorporate a diverse set of devices such as microelectromechanical systems (MEMS), optical, RF, and biochemical components into one package [3]. A common form of SiP integration is die stacking. This method of integration utilizes wire bonding, flip chip bonding, and embedded conductors, within the die itself, to make interconnects between different dies possible [4]. This has moved packaging schemes from the 2D planar level to 3D. Figure 1-2 illustrates the different uses of interconnects to build a SiP device.

Figure 1-2 3D Packaging Techniques. 1a&1b) Die stacking. 2) Flip chip bonding. 3) Stacked dies interconnected within the dies by Tungsten conductors. All images are taken from [1].

#### 1.1.1 SiP Market

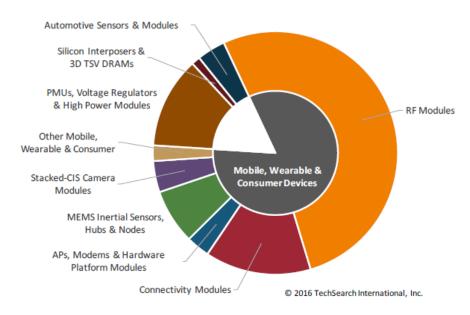

In the SiP market, RF modules account for 66% of the market distribution (Figure 1-3) [4]. As a result, proper shielding between interconnects, especially when using interconnects as shown in Figure 1-2, is becoming increasingly important in SiP manufacturing. Additionally, interconnects used in RF modules will require low inductance for good power distribution, and low transmission loss for signal distribution. This will continue to be a priority as pitch between interconnects decreases, and IO counts increase.

## 2016 SiP Market by Device Type (shares of packages shipped)

Figure 1-3 Break down of SiP market demands [4]. RF modules account for the majority the SiP market.

#### 1.2 Radio Frequency Waves and Microwaves

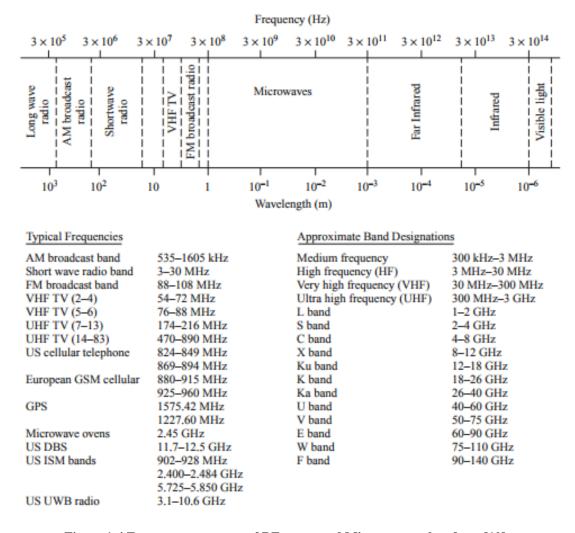

A primary focus for this thesis is packaging of high frequency modules. Radio frequency (RF) waves and microwaves typically have alternate current (AC) signals with frequencies between 100 MHz – 1000 GHz [6]. The electromagnetic spectrum shown in Figure 1-4 illustrate that RF frequencies consists of waves that range from Very High Frequencies (VHF) of 30 – 300 MHz to

Ultra High Frequencies of 300-3000 MHz. Microwaves consists of even higher frequencies usually covering a range between 3 - 300 GHz and with wavelengths on the order of 10 cm to 1 mm [6]. Due to the high frequencies of RF waves and microwaves, circuit elements cannot be analyzed using standard. Kirchhoff-style circuit theory, but instead through electromagnetic and transmission line theory. At these high frequencies voltage and current vary in magnitude and in phase along the physical lengths of devices that use RF and Microwave technology. This is especially true in microsystems where the wavelengths of AC signals are comparable to electrical lengths [6].

Figure 1-4 Frequency spectrum of RF waves and Microwaves taken from [10].

RF waves and Microwaves have unique properties that are utilized in military, science, and commercial applications [6]. In antenna and radar design high frequencies allow for more antenna gain and better target detection. For communication systems, RF waves and microwaves are not easily deflected by the ionosphere, making technology like GPS, weather analysis, and communication around the globe possible. Additionally, higher frequencies provide higher bandwidth capabilities which improve networking and communication systems. Lastly, the use of RF waves and microwaves have improved medical diagnostics as molecular resonances occur at high frequencies improving biomedical sensors and imaging [6].

Packaging devices that operate at these high frequencies can prove to be challenging as high frequency modules face hurdles that DC or lower frequency modules do not. These issues are addressed in more detail in chapter 4 of this thesis. The key problems packaging manufacturers face are parasitics, discontinuities, and electromagnetic interference (EMI) [7]. In this thesis focus will be spent on utilizing microcoaxial cables as a rapid integration method, with a focus on shielding to reduce EMI, and low inductance to enable efficient power distribution.

#### 1.3 Micro-Coaxial Interconnects for SiP RF Modules

Standard wire bonding, flip chip methods, and embedded die techniques are just a few of the methods that designers in the semiconductor industry are using to create RF SiP modules. Nuvotronics' Coaxial Waveguide, Hitachi Chemical Co.'s Multi-Wire Board, and BridgeWave and Kulicke & Soffa Industries' in-situ microcoax fabrication and attachment process are three technologies that employ the use of waveguides, insulated wires, and micro-coaxial cables as the primary mode of interconnects to enhance signal integrity for RF modules. These methods use clever attachment strategies, or automated wire bonding and routing technology to achieve high speed and reconfigurable integration. These three existing technologies have influenced an internal

research and development (IRAD) project at Draper named Miniature-Multi-Wire Systems (MMS) which has served as the basis for this Master's Thesis.

#### 1.3.1 Nuvotronics Coaxial Waveguide and Reconfigurable RF Components

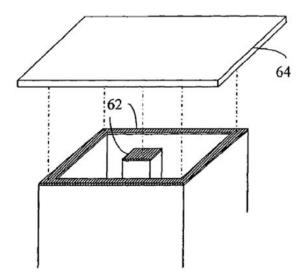

Figure 1-5 illustrates a fabricated coaxial waveguide microstructure with a rectangular cross section fabricated by Nuvotronics in 2003. This structure consists of an inner conductor surrounded by four walls that make up the outer conductor. Both conductors are separated and their structures are held in place by dielectric support members that are enclosed in some volume between the inner and outer conductor. The dielectric material of this coaxial waveguide is primarily air under vacuum enclosed in the space between the inner and outer conductor [8]. The waveguide is made to be used for signal transmission with a characteristic impedances between 30-70  $\Omega$ . The structure is made through various lithographic patterning and metal deposition steps, utilizing highly conductive metals such as Gold, Copper, Nickel and Aluminum [8].

Figure 1-5 Images of a coaxial waveguide microstructure taken from [8]. Schematic of inner and outer conductors, labeled as 62, enclosed by a passive or active device, labeled as 64, that will utilize the coaxial wave guide.

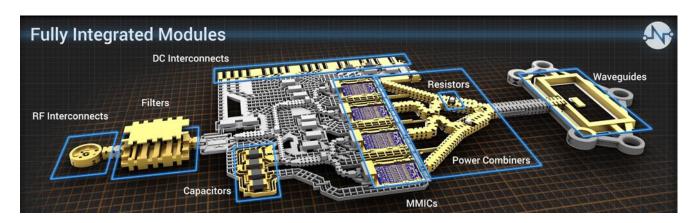

Nuvotronics incorporates the use of this coaxial waveguide structure with other micro machined structures such as RF filters, antennas, switches, inductors, capacitors, and other passive and active components (Figure 1-6). Each component is uniquely fabricated to have micro-mechanical interconnects that allow for assembly between other components. These attachments also allow for rearrangement within the RF module if new components are to be added or if components are to be removed or replaced [9].

Figure 1-6 Schematic of a fully integrated RF module by Nuvotronics. Micro sized interconnects are used to attach components to each other. These interconnects are reconfigurable. Figure taken from [9].

#### 1.3.2 Hitachi Chemical Co.'s Multi-Wire Board

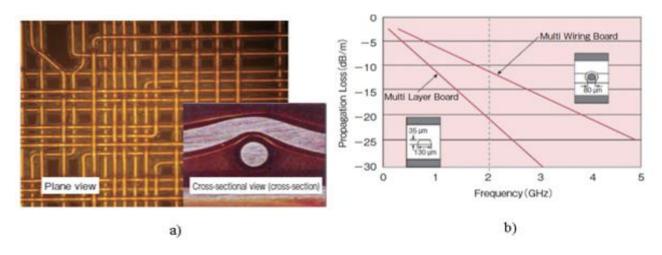

Hitachi Chemical Co.'s Multi-Wire board introduced in 2015 is a SiP technology that utilizes rapid routing of pre-fabricated wires to package microchips. Current capabilities include automated high-density routing of Copper wires insulated with Polyimide resin  $80 - 100 \mu m$  in diameter (Figure 1-7) and with wire lengths up to  $650 \mu m$ . Hitachi is capable of packaging chips with substrates that are up to  $6300 \mu m$  thick and up to substrate areas of  $330 \cdot 10^9 \mu m^2$ . These wires have been shown to have higher signal integrity relative to planar PCB technology of comparable dimensions illustrated in Figure 1-7. Propagation loss per length is  $25 \cdot 10^{-6} \, dB/\mu m$  up to 5 GHz [10].

Figure 1-7 a. Routed connections using Multi-Wire Board technology and a cross section of insulated Cu wire. 6b. Propagation loss (dB/m) of 2D planar multilayers with a cross sectional area of 4550 um<sup>2</sup>, and 3D coaxial geometry with a cross sectional area of 5027 um<sup>2</sup>. Images taken from [10].

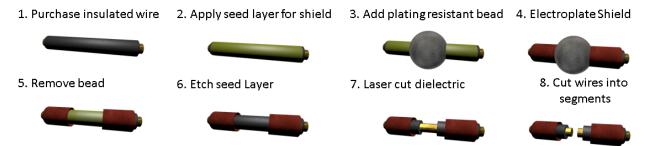

#### 1.3.3 In-Situ Fabrication and Attachment of Micro-Coax

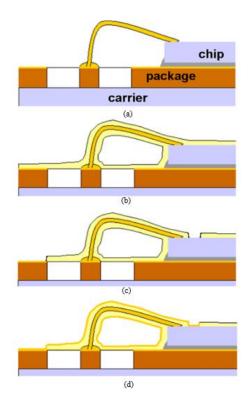

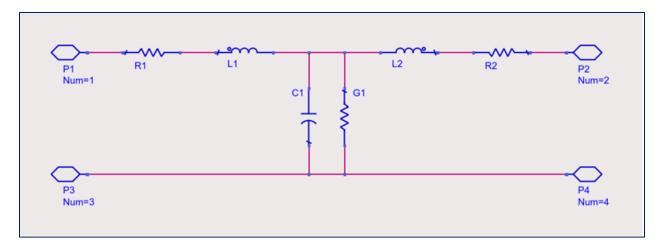

A third micro-coax integration strategy comes from Sean Cahill, Eric Sanjuan, and Lee Levine from BridgeWave Communications and Kulicke & Soffa Industries. The process, illustrated in Figure 1-8, was introduced in 2006 [11] and involves an in-situ signal coax fabrication and attachment strategy targeting characteristic impedances of 40  $\Omega$  and 50  $\Omega$ . The signal fabrication process involves: wire bonding Gold interconnects, using a conformal coating of Parylene C or Parylene N as a dielectric material, laser etching to expose ground paths, metalizing all wires by depositing a thin adhesion metal layer, and Gold plating a thick metal shield. Cahill, Sanjuan, and Lee have been successful at fabricating signal coax 92- 113  $\mu$ m in diameter and up to wire lengths of 2000  $\mu$ m. Transmission line performance reported in their work include transmission line losses of 0.00025 dB/ $\mu$ m and cross-talk isolation of 40-50 dB up to 50 GHz and with bond pitch sizes of 160-213  $\mu$ m [11].

Figure 1-8 Outline of Signal Micro-Coax Fabrication Known as an in-situ micro-coax fabrication and attachment strategy [11]. (a) Wire Bonding from a chip to package. (b) Dielectric coat. (c) Laser etch to expose ground path. (d) Metallization of shield.

#### 1.3.4 Miniature Multi-Wire Systems

An internal research and development (IR&D) project at Draper named Miniature Multiwire Systems (MMS) aims to use shielded microcoax for *all* component interconnects to eliminate the lengthy layout and fabrication processes associated with power and signal distribution. MMS final form of technology (Figure 1-9) would involve a process similar to wire bonding: a tool that is capable of spooling microcoaxial cables, which are fabricated beforehand in a reel to reel process, with in line shield stripping capabilities, and capable of bonding the core and shield at both ends

of the wire [12].

Figure 1-9 Illustration of MMS technology. Components are placed onto a substrate (grey) and interconnected together with micro-coax by an automated micro-coax bonder.

Current wires utilize dielectrics such as Parylene C, Polyeurethane, and Polyesterimide with conductors such as Copper, Gold, and Silver. For power distribution measured characteristic impedances are between  $2.87-16.7~\Omega$ . For signal distribution characteristic impedances are measured to be between  $33-81~\Omega$ . Cross-talk integrity is low at -60 dB up to 10 GHz.

A summary of coaxial transmission lines for SiP and their properties can be found in Table 1-1.

Table 1-1 Summary of Coaxial Transmission Lines for SiP and Their Properties

| Tuble 1 1 Summary of Country Transmission Emes for Sir and Their 1 toperates |                                    |                                                            |                          |                 |               |

|------------------------------------------------------------------------------|------------------------------------|------------------------------------------------------------|--------------------------|-----------------|---------------|

|                                                                              |                                    |                                                            | In-Situ                  | Hitachi's       | Nuvotronics'  |

|                                                                              | Thesis Work                        | MMS                                                        | MicroCoax                | Multi-Wire      | Waveguide     |

| Wire Type                                                                    | Power & Signal                     | Power & Signal                                             | Signal                   | Signal          | Signal        |

| Dielectric                                                                   | Parylene C<br>ALD HfO <sub>2</sub> | Polyesterimide<br>Polyurethane<br>Parylene C<br>Parylene N | Parylene C<br>Parylene N | Polyimide Resin | Air or Vacuum |

| Conductors                        | Gold                                                               | Copper<br>Gold<br>Sn/Ag Eutectic   | Gold                              | Copper                                 | Copper, Gold,<br>Nickel,<br>Aluminum |

|-----------------------------------|--------------------------------------------------------------------|------------------------------------|-----------------------------------|----------------------------------------|--------------------------------------|

| Measured Characteristic Impedance | Power: 0.07-3.5Ω<br>Signal:40-60 Ω                                 | Power:2.87-16.7Ω<br>Signal: 33-81Ω | 40-50Ω                            | 45-55Ω                                 | 30-70Ω                               |

| Measured<br>Cross-Talk            | -40 to -62 dB up to 26.5 GHz                                       | -60dB up to 10<br>GHz              | -40to -50 dB<br>up to 50<br>GHz   | n/a                                    | n/a                                  |

| Loss                              | Power: 0.004dB/ µm up to 12 GHz  Signal: 0.0001 dB/µm up to 12 GHz | n/a                                | 0.00025 dB/<br>μm up to 50<br>GHz | 25·10 <sup>-6</sup> dB/ μm up<br>5 GHz | n/a                                  |

#### 1.4 Contributions

Chapter 3 of this thesis is a paper being submitted to *iMAPS Journal of Microelectronics and Electronic Packaging*. This paper outlines design criteria for microcoaxial cables intended for power distribution. Design is centered around requirements in a power distribution network in which lower impedances are necessary (impedances less than 20  $\Omega$ ). Chapter 3 also outlines the fabrication process primarily used by MMS to create microcoax which differs from the fabrication process used in Chapter 4. The fabrication process highlighted in Chapter 3 is a first step towards a reel to reel microcoaxial fabrication process for an automated microcoaxial wire bonder. RF characterization methods primarily used for MMS are also highlighted in Chapter 3 with measured electrical properties of the first set of cables fabricated by Draper.

Chapter 4 of this thesis is a paper being submitted to *IEEE Components Packaging and Manufacturing Technology*. This paper is focused on utilizing a different fabrication process than the one discussed in chapter 3. This analysis contains the majority of contributions for this thesis

work. The main goals for this analysis was to expedite integration and characterization of microcoaxial cables for Miniature Multi-Wire Systems using an the in-situ microcoaxial fabrication and attachment process by Sean Cahill, Lee Levine, and Eric Sanjuan, that was described previously. This process has the advantage of not needing a new tool or new processing techniques to create micro-coax; instead it uses existing technology to do so. To extend some of the work that has been done previously, this thesis is focused on fabricating both power and signal coax with different thin dielectrics to achieve even lower impedances as well as thick dielectrics for proper signal distribution. This thesis work also outlines the characterization of both the electrical properties of each wire and cross-talk between wires.

Prior to both of those papers is Chapter 2 which is focused on providing some background theory that is used in all experimental and analytical work. A basic understanding of transmission lines, microcoaxial geometry and its effect on electrical performance, network theory, and data display techniques were necessary to properly characterize microcoax at high frequencies.

## 2 Background Theory

#### 2.1 Transmission Line Basics

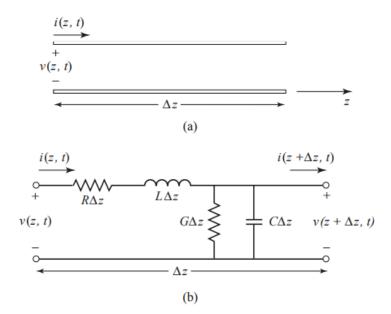

A transmission line is a distributed component where along its length, voltage and current may vary in magnitude in phase. Most transmission lines (i.e coaxial cables) can be represented by the distributed circuit seen in Figure 2-1. Each line has a length  $\Delta z$ , current I(z,t), voltage v(z,t) between two conductors, resistance (R) per length ( $\Omega/m$ ), conductance (G) per length (S/m), inductance (L) per length (S/m), and capacitance (C) per length (S/m). A Transmission line can be represented by multiple segments each with length  $\Delta z$ .

Figure 2-1 Basic Transmission Line Representation. a) Illustration of a transmission line with length  $\Delta z$ . b) Distributed circuit model of a transmission line. Image taken from [6].

Using the circuit described in Figure 2-1 it is possible to derive the following wave equations (1) for a voltage V(z) and I(z), using Kirchhoff's voltage and current laws, the telegrapher equations, and solutions to the wave equation [6]:

$$V(z) = V_0^+ e^{-\gamma z} + V_0^- e^{\gamma z}$$

$$I(z) = I_0^+ e^{-\gamma z} + I_0^- e^{\gamma z}$$

(1)

Where  $V_0^+$ ,  $V_0^-$ ,  $I_0^+$ , and  $I_0^-$  represent the amplitudes of the transmitted and reflected voltage and current waves,  $e^{-\gamma z}$  represents transmitted wave propagation,  $e^{\gamma z}$  represents reflected wave propagation, and  $\gamma$  represents the complex propagation constant. The complex propagation constant is described in (2) as [6]:

$$\gamma = \alpha + j\beta = \sqrt{(R + j\omega L)(G + j\omega C)}$$

(2)

where  $\alpha$  represents the attenuation constant of the line and  $\beta$  represents the phase constant of the line. Furthermore, a transmission line may be further characterized by its characteristic impedance,  $Z_0$ , which is defined as the ratio between the amplitudes of the voltage and current waves.  $Z_0$  is expressed in (3) as [6]:

$$Z_{0} = \frac{V_{0}^{+}}{I_{0}^{+}} = \frac{-V_{0}^{-}}{I_{0}^{-}} = \frac{R + j\omega L}{\gamma} = \sqrt{\frac{R + j\omega L}{G + j\omega C}}$$

(3)

The wavelength,  $\lambda$ , of a transmission line is defined in (4) as [6]:

$$\lambda = \frac{2\pi}{\beta} \tag{4}$$

The phase velocity,  $v_p$ , of the waves that propagate within the transmission line is defined in (5) as [6]:

$$v_{p} = \frac{\omega}{\beta} = \lambda f \tag{5}$$

For a lossless transmission line it is assumed that conductivity and dielectric losses resulting from R and G are equal to zero, and therefore  $\alpha$  is equal to zero. This can be true for metals with high conductivity, such as gold and copper, and for polymer dielectrics with low conductivities. This results in the following changes (6) to the definitions of  $\gamma$ ,  $Z_0$ ,  $\lambda$ , and  $v_p$  [6]:

$$\gamma = \alpha + j\beta = j\omega \sqrt{LC}$$

$$Z_0 = \sqrt{\frac{L}{C}}$$

$$\lambda = \frac{2\pi}{\omega \sqrt{LC}}$$

$$v_p = \frac{1}{\sqrt{LC}}$$

(6)

It is important to note that characterizing a transmission line this way assumes that the waves in the line propagate as transverse electromagnetic (TEM) waves [6]. TEM is a mode of propagation where the electric and magnetic fields are normal to the direction of propagation. In the case of Figure 2-1 waves propagate in the z-direction.

#### 2.2 Transmission Line Parameters for Coaxial Cables

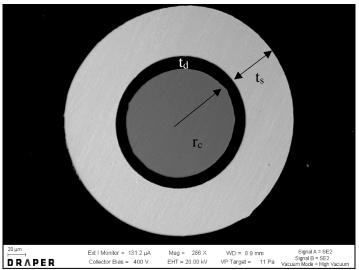

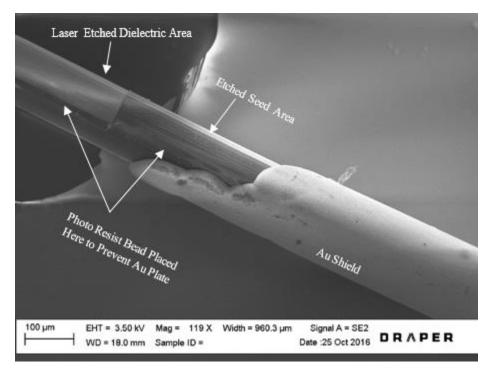

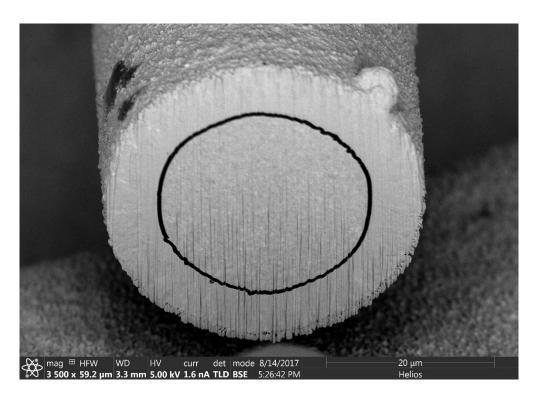

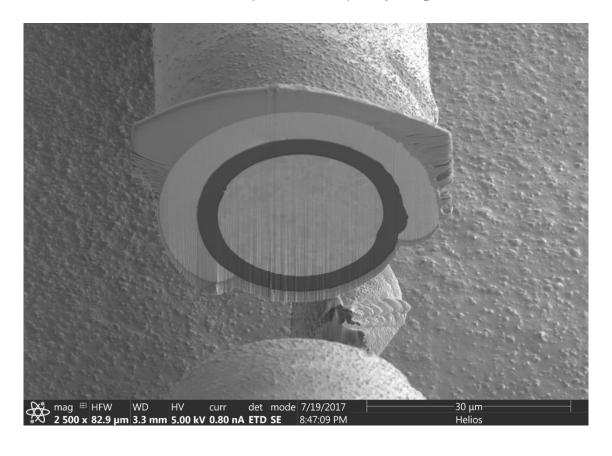

Figure 2-2 Scanning Electron Microscope image of cross section of fabricated micro-coax (fabricated for this work) with a 63.5 $\mu$ m radius core, 12  $\mu$ m Polyesterimide dielectric, and a 55  $\mu$ m gold plated shield. In this image  $r_c$  represents the radius of the core,  $t_d$  represents the dielectric thickness, and  $t_s$  represents the shield thickness.

Typical coaxial cable geometry (Figure 2-2) consists of an inner conductor (core), dielectric material (insulator), and an outer conductor (shield). Geometric, magnetic, and dielectric

properties of the coaxial cable will have direct influence on R, G, L, and C of the cable. In typical coaxial transmission lines it is assumed that the core and shield metals are highly conductive and weakly paramagnetic, the core and shield carry currents equal in magnitude but opposite in direction, and the magnetic field produced by the core is directed radially outward while the magnetic field produced by the shield is directed radially inward [12]. This typical behavior maintains the magnetic fields, produced by the wire, within the wire itself.

The resistance of a coaxial transmission line, R, represents conductivity losses of the cable and is defined in (7) as [6]:

$$R = \frac{R_s}{2\pi} \left( \frac{1}{r_c} + \frac{1}{r_c + t_d} \right)$$

(7)

where  $r_c$  is the radius of the core,  $t_d$  is the dielectric thickness, and  $R_s$  is the surface resistance of both the core and shield which is defined in (8) as [6]:

$$R_{s} = \frac{1}{\sigma \delta_{s}} \tag{8}$$

$\sigma$  is the conductivity of the core and shield and  $\delta$ , is the skin depth of both those conductors. The skin depth of a conductor is defined in (9) as [6]:

$$\delta_{s} = \frac{1}{\alpha} = \sqrt{\frac{2}{\omega \mu_{0} \mu_{r} \sigma}} \tag{9}$$

where  $\mu_0$  is the permeability of free space equal to  $4\pi \cdot 10^{-7}$  H/m and  $\mu_r$  is the magnetic permeability of the dielectric. It is important to note that skin depth is a function of frequency,  $\omega$ . Typically, at higher frequencies one can expect the resistance of a conductor to increase as the effective cross sectional area of the wire that carries current is essentially reduced due to the skin effect [6]. The

conductance, G, of a coaxial transmission line represents the dielectric losses of the cable and is defined in (10) as [6]:

$$G = \frac{2 \pi \omega \varepsilon_0 \operatorname{Im} \{\varepsilon_r\}}{\operatorname{ln} \left(\frac{r_c + t_d}{r_c}\right)}$$

(10)

where  $\varepsilon_0$  is the permittivity of free space and equal to  $8.85 \cdot 10^{-12}$  F/m and  $\varepsilon_r$  is the dielectric constant. The self-inductance between both the core and shield, L, of a coaxial transmission line is defined in (11) as [6]:

$$L = \frac{\mu_0 \mu_r}{2 \pi} \ln \left( \frac{r_c + t_d}{r_c} \right)$$

(11)

The capacitance, C, of a coaxial transmission line formed due to the spacing between the core and shield is defined in (12) as [6]:

$$C = \frac{2 \pi \varepsilon_0 \operatorname{Re} \{\varepsilon_r\}}{\ln \left(\frac{r_c + t_d}{r_c}\right)}$$

(12)

Throughout the analysis in this thesis focus will be spent characterizing L (equation 11), C (equation 12), and  $Z_0$  (equation 3) of different coaxial cables fabricated for the Miniature Multiwire Systems (MMS) packaging platform; assuming that conductivity and dielectric losses are at a minimum, and therefore we can neglect R (equation 7) and G (equation 10).

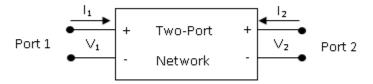

### 2.3 Two-Port Network Theory and Scattering (s) Parameters

Figure 2-3 Schematic of a two-port network.

Active or passive RF components may be analyzed using any number of ports in a network analysis. For analyzing and measuring coaxial transmission lines a two-port network analysis (Figure 2-3) is commonly used where the transmission line and its substrate is defined as a network. The advantage of measuring RF components this way is that the network can be fully characterized by measuring a set of parameters at each port (i.e each end of a wire) without knowing all the details within the network itself. As illustrated in Figure 2-3, each port may be excited with voltages,  $V_1$  and  $V_2$ , which will produce currents,  $I_1$  and  $I_2$ , within the network [13]. Admittance (y) and impedance (z) parameters are typical parameters used to describe a network as they directly relate currents,  $I_1$  and  $I_2$ , to voltages,  $V_1$  and  $V_2$ , via Ohm's law. However, for RF or microwave applications, where frequencies are high and voltages and currents are best described as waves that travel within the network, scattering (s) parameters are more suitable for analysis [6]. Scattering parameters describe the network by relating the incident,  $a_i$ , voltage waves at port i to the reflected,  $b_i$ , voltage waves at port i. The incident and reflected waves at each port, denoted as i (where for a two-port network i = 1,2), are defined in (13) as [13]:

$$a_{i} = \frac{Voltage\ w\ ave\ incident\ at\ port\ i}{\sqrt{Z_{0}}} = \frac{V_{i} + I_{i}Z_{0}}{2\sqrt{Z_{0}}}$$

$$b_{i} = \frac{Voltage\ w\ ave\ reflected\ at\ port\ i}{\sqrt{Z_{0}}} = \frac{V_{i} - I_{i}Z_{0}}{2\sqrt{Z_{0}}}$$

(13)

where  $V_i$  denotes the complex voltage at port i,  $I_i$  denotes the complex current at port i, and  $Z_0$  denotes an arbitrary reference characteristic impedance. The full two-port network is then described in (14) using s-parameters as [13]:

$$b_{1} = s_{11}a_{1} + s_{12}a_{2}$$

$$b_{2} = s_{21}a_{1} + s_{22}a_{2}$$

$$\begin{bmatrix} b_{1} \\ b_{2} \end{bmatrix} = \begin{bmatrix} s_{11} & s_{12} \\ s_{21} & s_{22} \end{bmatrix} \begin{bmatrix} a_{1} \\ a_{2} \end{bmatrix}$$

(14)

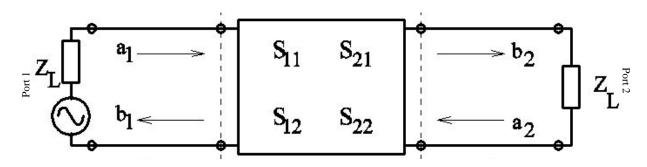

Figure 2-4 Two-Port Network with incident and reflected waves at each port. Also illustrated is the voltage source, V<sub>s</sub>, from the Vector Network Analyzer (VNA), source impedance and load Impedance, Z<sub>L</sub>, supplied by the VNA. Image taken from [13].

A Vector Network Analyzer (VNA) is capable of directly measuring s-parameters by inducing voltage waves  $a_i$  and  $b_i$  via voltage source  $V_s$  (Figure 2-4). To properly isolate each s-parameter a termination source impedance at port 1,  $Z_s$ , and a termination load impedance,  $Z_L$ , is introduced by the VNA (Figure 2-4). For example, to isolate  $S_{11}$ , voltage wave  $a_2$  is terminated by a setting  $Z_L = Z_0$  which sets  $a_2 = 0$ .  $S_{11}$  is then defined as a ratio of the reflected wave at port 1 ( $b_1$ ) and the incident wave at port 1 ( $a_1$ ) (15) [13]:

$$b_{1} = s_{11}a_{1} + s_{12} g_{2} = s_{11}a_{1}$$

$$s_{11} = \frac{b_{1}}{a_{1}}$$

(15)

Similar terminations are done to gather a full matrix of s-parameters. The definition of  $S_{11}$  can be broken down further by inputting the definitions of  $b_1$  and  $a_1$  (16) [13]:

$$s_{11} = \frac{b_1}{a_1} = \frac{\frac{V_1 - I_1 Z_0}{2\sqrt{Z_0}}}{\frac{V_1 + I_1 Z_0}{2\sqrt{Z_0}}} = \frac{V_1 - I_1 Z_0}{V_1 + I_1 Z_0}$$

(16)

Dividing by the current at port 1,  $I_1$ , results in (17) [13]:

$$s_{11} = \frac{\frac{V_{1}}{I_{0}} - Z_{0}}{\frac{V_{1}}{I_{1}} + Z_{0}} = \frac{Z_{1} - Z_{0}}{Z_{1} + Z_{0}}$$

(17)

Where  $Z_1$  denotes the input impedance at port 1 [13]. Similar relationships between s-parameters and impedance can be made which will be useful for understanding the Smith chart (described in later chapters). Another name for  $S_{11}$  and  $S_{22}$  are the reflection coefficients of the network. Whereas  $S_{12}$  and  $S_{21}$  are named the transmission coefficients of the network [13]. It is important to recall that since voltage and current waves carry magnitude and phase, s-parameters are complex values.

#### 2.4 Four-Port Network Theory

A four-port network analysis is useful for studying the coupling effects (cross-talk) between adjacent coaxial transmission lines. As frequency increases in a coaxial transmission line the magnetic fields produced by the core and shield conductors radiate and extend beyond the physical

dimensions of the coaxial cable partly due to the skin effect [12]. This magnetic radiation may be picked up or absorbed by nearby RF components (i.e another coaxial transmission line) [12]. In a four-port network the definition of incident (a<sub>i</sub>) and reflected waves (b<sub>i</sub>) remains the same (ports 1-4 will have their own incident and reflected waves), but the s-parameter matrix becomes larger since there is the added coupling relationship between wires [13]:

$$b_{1} = s_{11}a_{1} + s_{12}a_{2} + s_{13}a_{3} + s_{14}a_{4}$$

$$b_{2} = s_{21}a_{1} + s_{22}a_{2} + s_{23}a_{3} + s_{24}a_{4}$$

$$b_{3} = s_{31}a_{1} + s_{32}a_{2} + s_{33}a_{3} + s_{34}a_{4}$$

$$b_{4} = s_{41}a_{1} + s_{42}a_{2} + s_{43}a_{3} + s_{44}a_{4}$$

$$\begin{bmatrix} b_{1} \\ b_{2} \\ b_{3} \end{bmatrix} \begin{bmatrix} s_{11} & s_{12} \\ s_{21} & s_{22} \end{bmatrix} \begin{bmatrix} s_{13} & s_{14} \\ s_{23} & s_{24} \end{bmatrix} \begin{bmatrix} a_{1} \\ a_{2} \\ b_{3} \end{bmatrix}$$

$$\begin{bmatrix} b_{3} \\ b_{4} \end{bmatrix} \begin{bmatrix} s_{31} & s_{32} \\ s_{41} & s_{42} \end{bmatrix} \begin{bmatrix} s_{33} & s_{34} \\ s_{43} & s_{44} \end{bmatrix} \begin{bmatrix} a_{3} \\ b_{2} \\ b_{4} \end{bmatrix}$$

$$\begin{bmatrix} s_{31} & s_{32} \\ s_{43} & s_{44} \end{bmatrix} \begin{bmatrix} a_{4} \\ b_{4} \end{bmatrix}$$

The s-parameters outlined in blue and green are characteristic to each individual wire (no-coupling). These results would be the same s-parameters gathered from a two-port measurement of each individual wire. The s-parameters outlined in orange are the reflection and transmission coefficients of coupled wires that can be used to determine at which frequency the wires are well isolated from each other. Coupled transmission s-parameters (i.e S<sub>14</sub> and S<sub>23</sub>) are typically plotted on a magnitude vs. frequency plot. At low frequencies it is expected that the magnitude of coupled s-parameters is low (>-50 dB). At a certain frequency magnitude it is expected to increase as the radiated fields from one wire begin to induce a current in the adjacent wire.

#### 2.5 De-embedding

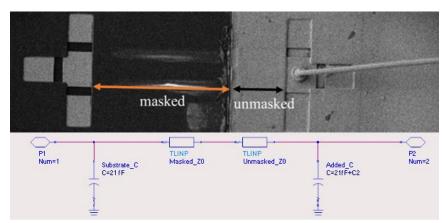

To test a coaxial cable's set of s-parameters using a Vector Network Analyzer (VNA) it is necessary to attach or fabricate the cables onto a test fixture. As a result, the full s-parameter matrix gathered from the VNA are that of the cable, often referred to as the device under test (DUT), and the test fixture. In order to properly characterize the transmission line parameters of the DUT the test fixture characteristics need to be removed from the full set of s-parameters. One of the methods used to remove the effects of the test fixture is known as de-embedding. De-embedding requires proper modeling or measurement of the test fixture to mathematically remove its effects [14].

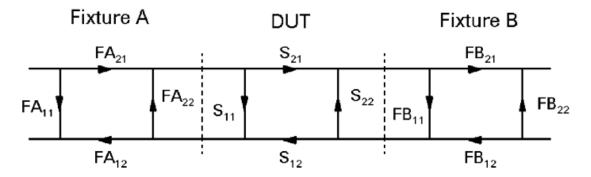

Figure 2-5 Signal flow graph of a two-port network analysis of a DUT and its test fixture effects at both ports [14].

To de-embed, it is assumed that the DUT, the test fixture component connecting the DUT to port 1 of the VNA (Fixture A), and the test fixture component connecting the DUT to port 2 (Fixture B) each contribute their own set of s-parameters. In Figure 2-5, fixture A's s-parameters are labeled as FA and fixture's B's s-parameters are labeled as FB. The full measurement of s-parameters gathered (S<sub>Measured</sub>) from the VNA are then represented by the following cascaded matrices (19) [14]:

$$\left[S_{Measured}\right] = \left[S_{FA}\right]\left[S_{DUT}\right]\left[S_{FB}\right] \tag{19}$$

Assuming that  $S_{FA}$  and  $S_{FB}$  are invertible,  $S_{DUT}$  may be extracted by a left and right multiplication of  $S_{FA}^{-1}$  and  $S_{FB}^{-1}$  which represent the matrix inverse of  $S_{FA}$  and  $S_{FB}$  (20) [14]:

$$\left[ S_{FA} \right]^{-1} \left[ S_{FA} \right] \left[ S_{DUT} \right] \left[ S_{FB} \right] \left[ S_{FB} \right]^{-1} = \left[ S_{FA} \right]^{-1} \left[ S_{Measured} \right] \left[ S_{FB} \right]^{-1} = \left[ S_{DUT} \right]$$

(20)

$S_{FA}$  and  $S_{FB}$  may be gathered directly, by separately measuring a test fixture without a DUT via a VNA known as measurement based De-embedding. Another method, which is a primary method used in this thesis, involves properly modeling the test fixture in software such as Advanced Design System (ADS) [14]; this method is known as model based de-embedding. Both methods will produce a set of  $S_{FA}$  and  $S_{FB}$  that can be inverted for de-embedding and extracting  $S_{DUT}$ .

#### 2.6 Plotting and Interpretation of S-Parameters

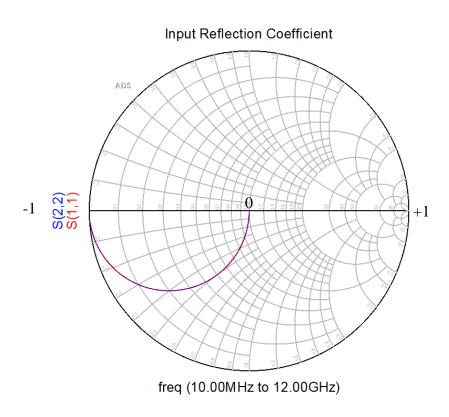

After gathering s-parameters from a Vector Network Analyzer (VNA), it is useful to plot sparameters for full interpretation of results. A VNA sweeps voltage over a range of frequencies and each frequency carries its own set of s-parameters. The most common way this information is presented is using a Smith chart plot and magnitude vs. frequency plot.

#### 2.6.1 Smith Chart

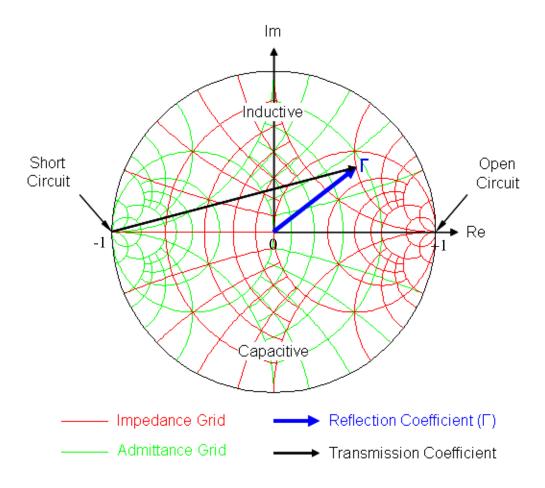

A Smith chart is a useful graphical tool used to plot reflection coefficients and relate them to impedance. Transmission coefficients may also be plotted on a Smith chart, but it is more common to plot reflection coefficients. The Smith chart overlays two coordinate systems: the first is a polar plot of complex s-parameters. The second is an impedance grid [15]. Recall the relationship described in (17) which relate the complex reflection coefficient to impedance [13]. This relationship is important since one of the end goals is to determine the impedance of the device under test (DUT). Additionally, the Smith chart is normalized to  $Z_0$ , the same  $Z_0$  defined in (13). Finally, each point on the Smith chart corresponds to a different frequency and its respective reflection coefficient.

Figure 2-6 Overview of a Smith Chart taken from [15].

Figure 2-6 outlines some important details of the Smith chart. Resistance, which is a real impedance, is located on the horizontal axis of the Smith chart. Inductance, which is a complex impedance, represents the top half of the Smith chart, and capacitance, which is also a complex impedance, represents the bottom half of the Smith chart [15]. A short circuit on the Smith chart is located far left since in order for a short circuit to be possible there should be a zero potential at the short. To get a zero potential the incident and reflected voltage waves should cancel each other out. This results in the magnitude of the reflection coefficient being equal to 1 (full reflection) with a phase of 180°. This is equivalent to saying that the reflection coefficient is equal to -1 on the Smith chart [15].

An open circuit on the Smith chart is located far right since in order for there to be an open circuit the incident and reflected voltages waves should be equal in magnitude and phase. This would result in the magnitude of the reflection coefficient being equal to 1 with a phase of  $0^{\circ}$ . This is equivalent to saying that the reflection coefficient is equal to 1 on the Smith chart [15]. The center of the Smith chart represents no reflections which means the DUT is matched perfectly to  $Z_0$ . This is equivalent to saying that the reflection coefficient is equal to zero [15].

Figure 2-7 Ideal capacitor behavior with minimal inductance from 10 MHz to 12 GHz.

Figure 2-7 illustrates how an ideal capacitor with minimal to no inductance is represented on a Smith chart. Frequency is swept clockwise such that at 10 MHz the plot begins at the center. Recall, that the circuit for a two port network connected to a VNA consists of the network (in this case a capacitor) and a load and source impedance. Typically, the load and source impedance are  $50~\Omega$  resulting in the Smith chart being normalized to a  $50~\Omega$  impedance. At low frequencies the

capacitor is open meaning the only impedance existing at port 1 or port 2 is the source or load impedance. A 50  $\Omega$  impedance is generally well matched with incoming voltage waves which result in zero reflections in the network. This explains why the Smith chart begins at the center. As frequency is swept, the capacitor impedance drops and it begins to behave as a short, which is why the scattering parameters sweep over to the left side of the Smith chart.

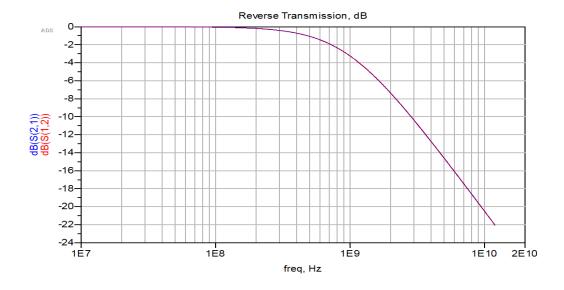

#### 2.6.2 Magnitude vs. Frequency Plot

Transmission coefficients are plotted on a magnitude vs. frequency plot (Figure 2-8). Since a coaxial cable is a passive RF component one should expect at low frequencies for the gain, or magnitude, of the transmission coefficient to be equivalent to 0 dB on a magnitude vs. frequency plot. 0 dB is a logarithmic representation of a transmission coefficient equal to 1. At low frequencies it is expected that a coaxial cable has minimal losses (no reflections) and thus is only transmitting voltage waves. At higher frequencies, as loss becomes more apparent one should expect the magnitude of the transmission coefficient to decrease. Since reflection and transmission coefficients are ratios, their magnitudes are typically less than 1. A magnitude less than 1 is represented on a magnitude vs. frequency plot as negative dB values.

Figure 2-8 Behavior of transmission coefficients on a magnitude vs. frequency plot of an ideal capacitor.

## 3 Characterization of Low Impedance Micro-Coaxial Cables for Power Distribution

#### 3.1 Abstract

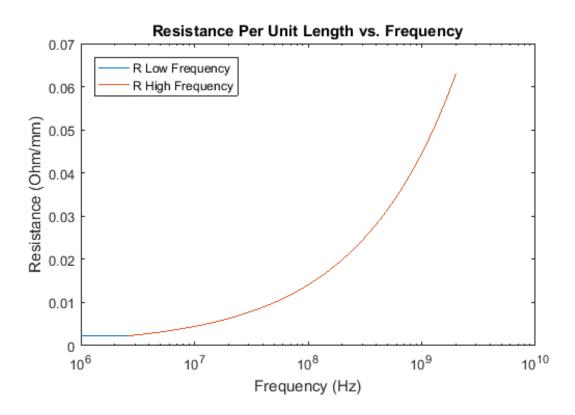

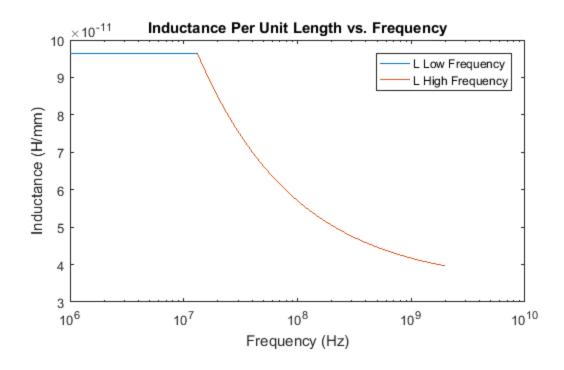

Low impedance micro-coaxial cables have been developed to supply power to microchips. These uniquely low inductance cables are enabled by a very thin dielectric compared to a conventional 50  $\Omega$  cable. These cables will be used in a novel packaging platform in which traditional interconnects are replaced by micro-scale coaxial cables. This method saves time, cost, and labor for small production volume and custom electronics, compared to conventional multilayered packaging techniques. These micro-coaxial cables are designed to have minimal impedance to meet the stringent power supply requirements of today's electronics. As a concrete example, we consider a Kintex 7 FPGA. To power this chip with interconnect lengths of 25 mm, voltage ripple less than 30 mV, and max current draw of 3.4W, a resistance of 3.20-6.40 mΩ/mm and an inductance of 12-15 pH/mm is needed. The tight voltage ripple constraint is what makes this device challenging to design power distribution for. One cable fabricated by Draper, to achieve these power requirements, is the focus of this paper. The Draper cable consists of a 127 µm Copper core, 12 μm polyester-imide dielectric layer, and 55 μm gold shield. The measured resistance per unit length at DC, inductance per unit length, capacitance per unit length, and characteristic impedance of the Draper cable are 2.0 m $\Omega$ /mm, 40 pH/mm, 118 pF/mm, and 6.56  $\Omega$  respectively.

#### 3.2 Introduction

A common architecture in packaging electronics is a 2D assembly of single chip modules on a printed circuit board (PCB) or other appropriate substrates. This packaging scheme has allowed designers to integrate multiple functions from various integrated circuits (ICs) in a single system.

However, this method has reached some of its limitations in fabrication. As the need for miniaturization and more functionality on a chip increases, 2D planar fabrication is challenging [16]. There are also increasing demands for complex power distribution, cost reduction, customization, and quick turnaround time for packaging technology [17]. Devices such as smartphones, pacemakers, automotive systems, and hybrid devices for the "Internet of Things (IoT)" are demanding more heterogeneous technology integration. As a result, designers are focusing their attention on making complex systems at the package level, by assembling multiple dissimilar chips into a package. This packaging platform is known as the System in Package (SiP) [17], which is different from System on a Chip (SoC). SoC is even more highly integrated, but less flexible and requires a longer design cycle.

SiP may incorporate a diverse set of devices such as microelectromechanical systems (MEMS), optical, RF, and biochemical components, into one package [16]. Some common forms of SiP integration are die stacking, wire bonding, and flip chip bonding. These methods have transformed packaging from the 2D planar level to 3D. Wire bonding has the advantage of being a rapid method of integration, however, one limitation is shielding between wires, needed to reduce cross-talk while maintaining required the impedance. The cross-talk issue is more prominent in RF modules that make up 65% of SiP packages [17], and thus the need for good signal and power integrity for these modules is increasingly important especially as IO counts, pitch, and miniaturization.

Previously described wire bonding and flip chip methods have been extended by some in the semiconductor industry to include integrated shields. Two technologies that employ the use of coaxial structures as the primary mode of interconnects to enhance signal integrity for RF modules

are Nuvotronics' Coaxial Waveguide [18] and BridgeWave and Kulicke & Soffa Industries' wirebond based micro-coaxial interconnects [20]. Hitachi Chemical Co.'s Multi-wire Board [9] demonstrates a rapid wire-only interconnect system using insulated wires. All three integration platforms have been designed with impedances between 30-70  $\Omega$ . However, to fully eliminate the need for lithographically patterned circuit layers, power distribution, which requires lower impedance coax, also needs to be addressed.

We have examined the existing layout and fabrication processes for SiP device and it appears that there are two major lead-time and cost drivers. First, finalizing a layout can take months due the need for multiple iterations because designs fail in simulation. Second, the multi-step microfabrication of the substrate can take weeks or months, due to multi-layer lithography and/or lamination steps, which can take days at a time and are not flexible to rapid changes in interconnect design often needed for custom and editable circuits. To minimize the time it takes to progress from an electrical schematic to a built, testable device, we propose using shielded microcoax for all interconnects. This eliminates the need for lengthy simulation and layout iterations. Fabrication time is also saved because the interconnects are fabricated with a single tool that resembles a modified wire bonder, capable of stripping and attaching micro-coaxial cables. The implementation of coax for signal distribution with impedance ranges between  $30 \,\Omega$ - $70 \,\Omega$  is well understood and has previously been studied for RF applications [6]. In this paper, we describe design criteria, fabrication methods, and RF characterization of micro-coax for power distribution with substaintially lower impedances than previously reported in the literature, <10  $\Omega$ .

### 3.3 Low Impedance Microcoax Design

Replacing traditional planar interconnects with micro-coaxial cables requires unique design considerations. Design is centered around a power distribution network (PDN) where a target impedance value can be used to design proper coaxial geometry for a given device. Target impedance values can then be related back to coaxial geometry, dielectric properties, and metal conductivity of the core and shield, which each influence the electrical properties of coax. Of particular interest is the resistance and inductance of micro-coaxial cables at near DC and at high frequencies due to its impact on a PDN.

#### 3.3.1 Case Studies of a Power Distribution Network

A power distribution network (PDN) may consist of multiple components, all of which are responsible for distributing power and handling return currents of a system. Components may include sources such as batteries or local decoupling capacitors, package leads, interconnects such as wire bonds, traces, vias, solder joints, or metalized pads on a chip. A key difference of a PDN compared to signal distribution is that the PDN is global and fully coupled across the system. Therefore, any component may have an effect on the whole delivery network [21]. For this analysis the major contributing elements in a PDN will be the resistance and inductance of micro-coaxial cables.

In order to focus the design space for developing micro-coaxial cables for a PDN, we chose the Kintex 7 FPGA as a case study for power handling. This system has demanding power requirements: needing 3.4 W at 1.0 V and a voltage ripple tolerance of less than 30 mV [22]. A PDN model of this system can be seen in Figure 3-1 where V<sub>Source</sub> represents a constant 1.0 V supply, R<sub>Budget</sub> represents the allowable resistance of a micro-coaxial cable in the PDN, L<sub>Budget</sub> represents the allowable inductance of a micro-coaxial cable in the PDN, and I<sub>Sink</sub> represents the current sink of the Kintex 7.

Figure 3-1 PDN Used to Estimate R<sub>budget</sub> and L<sub>budget</sub> for the Kintex 7 FPGA

The on chip capacitance is estimated by using the following relationship [21]:

$$C_{Chip} = \frac{\varepsilon_0 \varepsilon_{r_- die} A_{tdie} P_{gate}}{r_{oxide}}$$

(21)

Where  $C_{Chip}$  is the on chip capacitance,  $\varepsilon_{r\_die}$  is the dielectric constant of the chip oxide, which for this FPGA is 3.9,  $A_{tdie}$  is the die area taken up by the core transistors estimated to be 1 cm<sup>2</sup>,  $P_{gate}$  is the percentage of gate area estimated in [21] as 10 percent. This 10 percent estimate is taken from a general rule of thumb that not the entire die area makes up the transistor gate area. It is assumed that the on die capacitance is due only to its p and n junctions.  $r_{oxide}$  is the ratio of the gate oxide thickness to channel length estimated in [21] as 2 percent. This 2 percent estimate is taken from a general rule of thumb that with current transistor technology the gate oxide thickness is about 2 nm per 100 nm of channel length. This results in a  $C_{chip}$  of 600 nF.

The total impedance contributions of this PDN due to  $R_{Budget}$ ,  $L_{Budget}$ , and  $C_{Chip}$  is known as  $Z_{pdn}$ . The goal of PDN design is to minimize  $Z_{pdn}$  through specifying geometric and material properties to ensure enough battery voltage appears at the chip. Additionally, small  $Z_{pdn}$  will minimize voltage ripple,  $V_{ripple}$ , occurring at the chip which could lead to heating of components and distortion [20]. In the chip's idle state and during operation  $I_{Sink}$  may vary over time resulting in a varying voltage at the chip; this variation is known as voltage ripple.  $Z_{pdn}$  may be bounded as:

$$Z_{pdn} < \frac{V_{ripple}}{\Delta I} \tag{22}$$

Where  $V_{ripple}$  should be  $\leq$ 30 mV for the Kintex 7 FPGA, and  $\Delta I$  is the dynamic current. For a 3.4 W requirement and a 1.0 V voltage source, the max current that the chip may draw at any moment is 3.4 A. The chips static current is  $\sim$ 0.4 A and the transient current is 3.0 A [22]. We assume that the max current differential,  $\Delta I$ , occurs from the idle state to the start of operation. From this we estimate  $\Delta I$  is 3.0 A. This is a conservative approach as it assumes that the rise time of the chip from idle state to operation is small. For this analysis we assume the rise time is 10 ns.

Using (22), a  $V_{ripple}$  of 30 mV results in a maximum  $Z_{pdn}$  of 10 m $\Omega$ . To package the Kintex 7 FPGA using micro-coax a total of 16 wires are needed. For 16 wires the maximum impedance for each wire,  $Z_{pdn\_wire}$ , is 160 m $\Omega$ . Generally, due to the mutual inductance between wires, assuming that each wire contributes the same impedance is not a good assumption. However, because these wires are shielded, the assumption that mutual inductance is minimal is reasonable for this PDN analysis. This is one advantage of micro-coax.

To determine the appropriate sizing for the core, dielectric and shield of a power distribution coax for the Kintex 7, we must establish appropriate value ranges for  $R_{budget}$  and  $L_{budget}$  given that  $Z_{pdn\_wire}$  must be below 160 m $\Omega$ .  $R_{budget}$  will be directly correlated with the shield and core metal thickness tolerances, and  $L_{budget}$  will establish the allowable dielectric thickness for a given length of wire.  $R_{budget}$  and  $L_{budget}$  can be studied parametrically.

As a first case study,  $R_{Budget}$  is set to meet  $Z_{pdn}$  exactly and  $L_{Budget}$  is adjusted until the frequency response of  $Z_{pdn}$  is critically damped. Simulating this response in Advanced Design System (ADS) using the circuit in Figure 3-1, values for  $R_{Budget}$  and  $L_{Budget}$  are estimated as 160 m $\Omega$  and 320 pH

respectively. In Figure 3-2 the frequency response of  $Z_{pdn}$  is shown up to 1 GHz.  $Z_{pdn}$  is indicated to be 10 m $\Omega$  at frequencies lower than 19 MHz before being damped at higher frequencies. Also shown in Figure 3-2 is the time domain response of voltage ripple at the chip. Voltage ripple for this case remains below 30 mV.

Figure 3-2 Frequency of Zpdn up to 1 GHz (Left) and Time Domain voltage ripple response (Right) simulated in ADS with R Budget equal to  $160m\Omega$  and LBudget equal to 320 pH.

As a second case study,  $R_{Budget}$  is reduced to 80 m $\Omega$ . A higher  $L_{Budget}$  of 380 pH is allowable and maintains  $Z_{pdn}$  below 10 m $\Omega$ . The frequency response of  $Z_{pdn}$  can be seen in Figure 3-3. This low  $R_{Budget}$  and higher  $L_{Budget}$  produces a resonant peak at 38.40 MHz. For this case, voltage ripple maintains below 17 mV.

Figure 3-3 Frequency of Zpdn up to 1 GHz (Left) and Time Domain voltage ripple response (Right) simulated in ADS with R Budget equal to 80 m $\Omega$  and LBudget equal to 380 pH.

The average wire length needed to package the FPGA Kintex 7 with 16 Micro-Coaxial cables is 25 mm. This results in a  $R_{Budget}$ , using case 1 and case 2, of 3.20-6.40 m $\Omega$ /mm and an  $L_{Budget}$  of 12.8-15 pH/mm. These are the target specifications that drive design of the power distribution with micro-coax.

# 3.3.2 Resistance, Inductance, Characteristic Impedance and Capacitance of Coaxial Cables

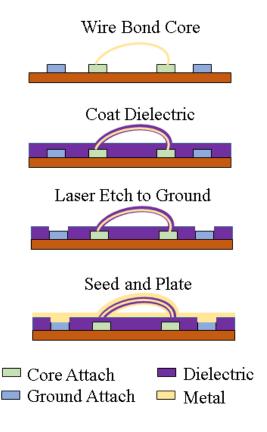

Figure 3-4 Scanning Electron Microscope cross section of fabricated micro-coax (this work) with a  $63.5\mu m$  radius core, 12  $\mu m$  Polyesterimide dielectric, and a 55  $\mu m$  gold plated shield.

We now need to relate the electrical performance goals to coax geometry. A cross section of a fabricated micro-coaxial cable is seen in Figure 3-4. Coaxial cable geometry consists of an inner conductor (core), dielectric material, and an outer conductor (shield). Geometric properties, magnetic and dielectric properties, will have an influence on the resistance, inductance, capacitance, and characteristic impedance of the cable. A table of important properties can be seen in Table 3-1:

**Table 3-1 Important Properties of Coax That Influence Electrical Properties**

| Parameter          | Value                                                     | Units |

|--------------------|-----------------------------------------------------------|-------|

| r                  | Core Radius                                               | μm    |

| t <sub>d</sub>     | Dielectric thickness                                      | μm    |

| $t_{\rm s}$        | Shield thickness                                          | μm    |

| $ ho_{c}$          | Core Resistivity                                          | Ω·cm  |

| $ ho_{ m s}$       | Shield Resistivity                                        | Ω·cm  |

| $\mu_0$            | Magnetic Permittivity Free Space = $4\pi \cdot 10^{-7}$   | H/m   |

| $\mu_{\rm r}$      | Magnetic Permittivity Constant = 1                        |       |

| $\epsilon_0$       | Electric Permittivity Free Space = 8.85·10 <sup>-12</sup> | F/m   |

| $\epsilon_{\rm r}$ | Dielectric Constant                                       |       |

| l                  | Wire Length                                               | mm    |

The DC resistance,  $R_{DC}$ , of a coaxial cable can be expressed as the sum of the core resistance,  $R_{core}$ , and the shield resistance,  $R_{shield}$ , both normalized to wire length [23]:

$$\frac{R}{l} = \frac{R_{core}}{l} + \frac{R_{shield}}{l} \tag{23}$$

At DC  $R_{core}$  and  $R_{shield}$  are only functions of wire geometry. The total resistance at DC,  $R_{DC}$ , per unit length in  $\Omega/m$  becomes:

$$\frac{R_{DC}}{l} = \frac{R_{core}}{l} + \frac{R_{shield}}{l} = \frac{\rho_c}{\pi r_c^2} + \frac{\rho_s}{\pi \left[ (r_c + t_d + t_s)^2 - (r_c + t_d)^2 \right]}$$

(24)

To determine the core radius,  $r_c$ , we assume that the core and shield metals of the microcoaxial wire will carry equal magnitudes of current. From this we may assume that the core and shield metals will split  $R_{Budget}$ . For a maximum  $R_{Budget}$  of 6.40 m $\Omega$ /mm we assume that the core metal should carry a DC resistance of 3.20 m $\Omega$ /mm. Using the definition of  $R_{core}$  in (24) and a resistivity of copper of 1.68·10<sup>-8</sup>  $\Omega$ ·m [24], the core radius of microcoax should be 41.0  $\mu$ m or greater to

maintain below the maximum core resistance of 3.20 m $\Omega$ /mm. We choose copper as our core material for the wires discussed in this paper since it has a high electrical conductivity.

To determine the shield thickness we must first determine a dielectric thickness. This can be done using  $L_{Budget}$ . The inductance, L, per unit length is:

$$\frac{L}{l} = \frac{\mu_0}{2\pi} \ln \left( \frac{r_c + t_d}{r_c} \right)$$

(25)

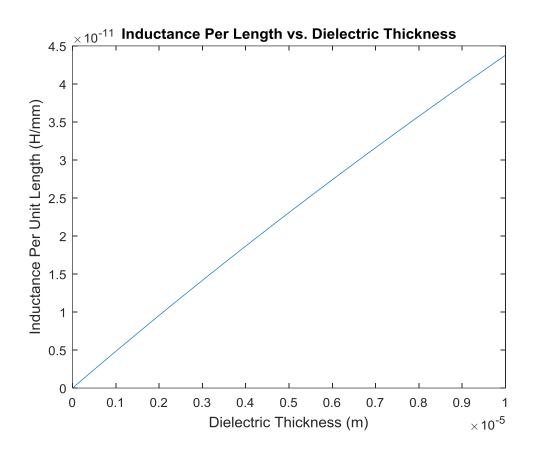

Given an  $L_{Budget}$  of 13-15 pH/mm and an  $r_c$  of 41.0  $\mu$ m it is possible to determine the necessary dielectric thickness for microcoax. A plot of inductance per unit length versus dielectric thickness can be seen in Figure 3-5 Inductance per unit length in H/m versus dielectric thickness determined by using (25). To target an inductance of 15 pH/mm or less, the maximum allowable dielectric thickness is 3.0  $\mu$ m. It is important to note that this is true for a dielectric material that is not ferromagnetic, such that  $\mu_r$  is 1.0.

Figure 3-5 Inductance per unit length in H/m versus dielectric thickness determined by using (25).

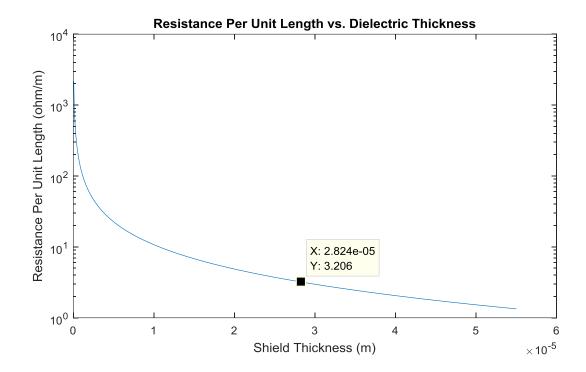

Given a core radius of 41.0  $\mu$ m and a target dielectric thickness of 3.0  $\mu$ m we can determine the shield thickness using the definition of  $R_{shield}$  described in (24). Since the core and shield will be splitting  $R_{Budget}$  the shield thickness can be determined by targeting a shield resistance of 3.20 m $\Omega$ /mm. For the wires in this paper we are interested in using a gold shield as we will later describe is possible to electroplate on dielectrics with an adhesive metal layer. The resistivity of our electroplated gold is 3.30·10<sup>-8</sup>  $\Omega$ m [25]. A plot of resistance per unit length versus shield thickness can be seen in Figure 3-6. To target a shield resistance of 3.20 m $\Omega$ /mm or less a shield thickness of 28.0  $\mu$ m or greater is required.

Figure 3-6 Resistance per unit length in H/m versus shield thickness determined by using (24).

Another important property of a coaxial transmission line is the characteristic impedance of the cable. Most generally, the characteristic impedance,  $Z_0$ , is derived from the telegrapher equations as [26]:

$$Z_{0} = \sqrt{\frac{R + j\omega L}{G + j\omega C}}$$

(26)

Where for a coaxial cable R is the total resistance per unit length  $(\Omega/m)$ , L is the total inductance per unit length (H/m), G is the conductance per unit length (S/m), and C is the total capacitance per unit length (F/m). For low loss dielectrics and low loss conductors the characteristic impedance simplifies to the following as R and G are minimal [26]:

$$Z_{0} \cong \sqrt{\frac{L}{C}} \tag{27}$$

Where the capacitance, C, per unit length, F/m, is [25]:

$$\frac{C}{l} = \frac{2\pi\varepsilon_0\varepsilon_r}{\ln\left(\frac{r_c + t_d}{r_c}\right)}$$

(28)

Characteristic impedance and capacitance are other electrical properties that we are capable of measuring and serve as good values to compare measurements to analytical results. A summary of target microcoaxial geometry can be seen in Table 3-2.

Table 3-2 Summary of Target Microcoaxial Geometry for Fabrication Given PDN Requirements of RBudget and LBudget

| Parameter      | Target Value | Notes                                                                                                                         |

|----------------|--------------|-------------------------------------------------------------------------------------------------------------------------------|

| r <sub>c</sub> | >41µm        | Determined using a core $R_{Budget}$ of 3.20 m $\Omega$ /mm, copper core material, and the definition of $R_{core}$ in (24)   |

| t <sub>d</sub> | <3.0 μm      | Determined using $L_{Budget}$ of 15 pH/mm and the definition of $L$ in (25)                                                   |

| $t_{\rm s}$    | >28 μm       | Determined using a shield $R_{Budget}$ of 3.20 m $\Omega$ /mm, gold shield material, and the definition of $R_{core}$ in (24) |

For a conservative approach, it is desired to pick a larger core radius greater than 41  $\mu m$  and a larger shield thickness greater than 28  $\mu m$  to reduce the overall resistance of micro-coax. A lower resistance will keep micro-coax below the target characteristic impedance of 160 m $\Omega$  per wire (10 m $\Omega$  total for the entire device being packaged with 16 micro-coaxial cables). Similarly, a thinner dielectric than 3.0  $\mu m$  is desired to minimize micro-coax inductance and also keep characteristic impedance below 160 m $\Omega$  per wire.

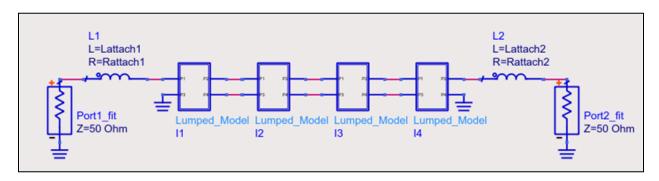

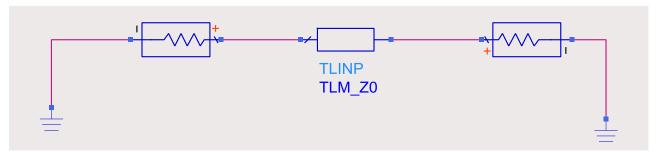

### 3.4 Low Inductance Microcoax Fabrication