# Development of LED Driver Circuit Architectures for Future Generation Visible Smart Lighting Networks, Combining High-Speed Data Communication and Illumination Control

A dissertation submitted by

Ali Mirvakili

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

Tufts University

February 2015

$\bigodot$  2015, Ali Mirvakili

Advisor: Prof. Valencia Joyner Koomson

For my parents

## Abstract

With the development of semiconductor-based light generated by light-emitting diodes (LEDs), the second generation of lighting known as solid state lighting (SSL) has been shown to provide greater energy efficiency compared to the conventional incandescent light bulb. The vision for SSL technology is to attain the full potential of light by capitalizing on energy efficiency, long lifetime, and improved sustainability. The light modulation capability of LEDs has produced considerable interest in the use of solid-state illumination systems for data communication. Visible light communication (VLC) has a number of unique advantages from ecological and human health perspectives; and the optical range is free from regulation, resulting in high data rate channels. Dual-purpose indoor LED lighting systems providing illumination control and data communication requires novel LED driver circuit architectures to realize the plethora of VLC-based applications envisioned for future lighting networks. This thesis presents research on novel driver circuit architectures for VLC applications. The driver circuit architecture presented in this work overcomes the modulation bandwidth limitation by providing a feedback control loop to maintain the DC-DC converter output voltage independently of the LED drive signal to control data modulation and dimming. The main challenge of implementing a fast link in VLC networks is emanated from the inherent bandwidth limitations of LEDs. In this work the conventional methods of extending the bandwidth of LED drivers are reviewed and proposed topologies are introduced. Seven distinct methodologies of negative impedance converter (NIC), equalization techniques, pulse shaping, peaking, pole-zero cancellation, time-interleaved LEDs, and 16-level PAM are presented. The concept of NIC is reviewed and two different modes of

fixed and floating structures with their corresponding proposed LED drivers are introduced. Pre- and post-equalization techniques are analyzed such as multiple resonant, and active and passive equalizations are methods, which compensate the roll-off in the transfer function of raw-LED, leading to bandwidth extension. An LED driver based on a pulse shaping circuit topology is presented which enhances the overall bandwidth of the VLC link by shortening the rise and fall times. The next method for bandwidth enhancement is peaking. Different peaking techniques such as shunt, series, (bridged) shunt-series and triple resonant peaking techniques are reviewed and a new technique called bridged-shunt-zero peaking is proposed. A peaking technique called bridged-shunt-zero peaking is presented in this work, which is suitable for incorporation into the LED driver circuit design. An LED driver with enhanced bandwidth using the pole-zero cancellation methodology is presented to overcome the inherent bandwidth limitation of LED device. Time-interleaved LEDs is yet another trend in compensating the low bandwidth of LEDs. In this method each binary input is sent with a fixed delay and it can be detected by processing the received signals. Finally, an LED driver that implements 16-level PAM signaling using a  $4 \times 4$  array of LEDs is described, yielding an increase in the data transmission rate by 4 times.

# Acknowledgments

I would not have been able to finalize this research without help of first and foremost my advisor Prof. Koomson for my personal and professional developments. I cannot overstate how influential and supportive Prof. Koomson has been. I can only aspire to her depth of continuous encouragement, mentorship and support. Her inspiration was essential to the completion of this dissertation. I would like to thank my thesis committee Prof. Aleksandar Stankovic, Prof. Mark Cronin-Golomb, and Mr. Eko Lisuwandi for their time and dedication. They have offered insightful suggestions on this work.

I also would like to thank the faculty and students of the smart lighting ER-C center. At RPI, I would like to thank Prof. Karlicek for being a high impact director. I also would like to thank Profs. Dutta, Chow, Parsa, Hella, Dr. Fahs, and Dr. Nakhkoob for offering great research tips. At RPI I also would like to thank Sina, Hafez, Kumar, Sagar, Sruthi, Zhibo, Jun, and Pengfei. At BU I would like to thank Prof. Little for his great help, support and dedication, Dr. Elgala for offering invaluable research thoughts, and Dr. Borogovac. At BU I also would like to thank Michael, Pankil, Jimmy, Yuting, and John. At UNM I would like to thank Prof. Zarkesh-Ha, and also Javad and Mottaleb. And special thank to ERC staffs Diane, Silvia, and Michelle. I also would like to thank Profs. Kavehrad and Ghassemlooy for their valuable research tips. I would like to thank my lab fellows Saroj, Saber, Chirag, Enjin, Chenguang, Hassan, Ninrat, Pooria, Pramod, Ritika, Ruida, Sungkil, Shide, Sam, Michael, Li, Wangren, Jian, Kyoungchul, Robert, Guoqing, Meera and Robbie. It was a good opportunity to work with Chiamaka, Nana, Stephen, Ilankir and Chelsea over the summer breaks. I also would like to thank the friends at ECE department Alireza, Hamideh and Mahdi, Anjali, Yuping, Rafik,

Bob, Fridrik, Benson, Nahid, Chen, and Okuary. And I would like to thank Saeed, Ehsan, Mohammadreza, Alireza, Mashhood, Bilal, Amin, Nauman, Saad, Zafar, Amin, Morteza, Javad, Iman, Arash and Haaris for all their help and support. I would like to thank Prof. Sonkusale for teaching analog and mixed signal circuit. I also would like to thank Profs. Afsar, Panetta, MacLachlan, Hopwood, Miller, Noonan, and Lasser. The Administrative Staffs at Halligan were the source of help and I would like to thank Miriam, Ilse, and Renee for their great assistance. I want to state my appreciation to George for his support in handling any technical and departmental matters. Any software and hardware problem solved by the help of great talents at Halligan and I would like to thank George, Erik, Mike, Jonathan, and Patrick. The international center advisors are amongst the best and they were always eager to welcome and help and I would like to thank Jane, Lois, Hannah, Naoko, and Whitney. The help of career center advisors was exceptional; I would like to thank Robin and Nicole for their great support and their great career consulting. I also would like to thank the friends and families of Drs. Neilforooshan, Mosallaei, Kermani, Ebrahimi, Ajoodanian, Alam, Badrossamay, Ebrahimi, Elahi, Hashempour, Rismani, Azadi, Khoshchehreh, Araghchini, Sahlodin, Agheli, Dehghani, Khaleghi, Askariveh, Mobin, Hedavatzadeh, Yarmand, Ghaemi, Rezaian, Sadraey, Negahbanazar, Zarghami, Mianabadi, Ebrahimnejad, Bahrehdar, Abnoos, Moaddel, Aref, Sadeghipor, Sharifi, Dolaty, Azimi, Moazami, Rashidi, Mohammadi, Jahanbakht and Jalalifar for putting time and effort.

The most important, I would like to thank my grandmothers, NanaAgha Khanom (God bless her), and NanaBibi Khanom which no words can describe their excellence as well as my respected father, my respected mother and my respected brother for all their great support without which my success was under question.

Ali Mirvakili

Tufts University February 2015

# Contents

| Abstra  | $\operatorname{ct}$                               | iii          |

|---------|---------------------------------------------------|--------------|

| Ackno   | wledgments                                        | $\mathbf{v}$ |

| List of | Tables                                            | xi           |

| List of | Figures                                           | xii          |

| Chapt   | er 1 Introduction                                 | 1            |

| 1.1     | Motivation                                        | 1            |

| 1.2     | Thesis Organization                               | 3            |

| Chapt   | er 2 Visible Light Communication using White LEDs | 5            |

| 2.1     | Introduction                                      | 5            |

| 2.2     | Visible Light Communication (VLC)                 | 6            |

| 2.3     | Fundamental Analysis for VLC                      | 7            |

|         | 2.3.1 Basic Photometric Units                     | 8            |

|         | 2.3.2 Illuminance of LED Lighting                 | 12           |

|         | 2.3.3 Received Power from LED Lights              | 13           |

|         | 2.3.4 Received Power of Reflected Light           | 14           |

|         | 2.3.5 Optical Wireless Channel                    | 14           |

| 2.4     | White LED                                         | 15           |

|         | 2.4.1 Types of White LEDs                         | 16           |

| 2.5     | LED Modulation Characteristics                    | 17           |

|      | 2.5.1 Rise and Fall Times, and Bandwidth                    | 17        |

|------|-------------------------------------------------------------|-----------|

| 2.6  | LED Transient and Frequency Response                        | 19        |

|      | 2.6.1 Diffusion Capacitance $C_d$                           | 20        |

|      | 2.6.2 Frequency Response of a Forward Biased LED            | 20        |

|      | 2.6.3 Response Time of LED Neglecting $C_d$                 | 21        |

|      | 2.6.4 Response Time of LED Considering both $C_d$ and $C_s$ | 23        |

|      | 2.6.5 Transient Behavior: Closed-form Calculation           | 25        |

|      | 2.6.6 Low-Frequency Response of LED                         | 27        |

| 2.7  | Conclusion                                                  | 28        |

| Chap | ter 3 Linear and Switch-mode Regulator for LED Drivers      | 30        |

| 3.1  | Introduction                                                | 30        |

| 3.2  | LED Driving Techniques                                      | 31        |

|      | 3.2.1 Amplitude-Mode Driving Technique                      | 31        |

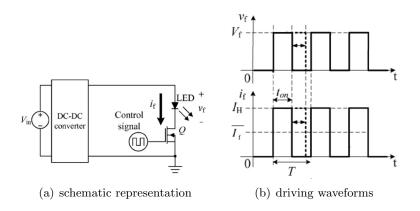

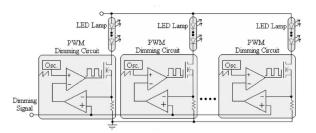

|      | 3.2.2 PWM-Mode Driving Technique                            | 32        |

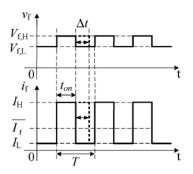

|      | 3.2.3 Bilevel Current Driving                               | 34        |

| 3.3  | Linear Regulator                                            | 36        |

| 3.4  | Swithing Mode Regulator                                     | 41        |

|      | 3.4.1 Voltage Mode vs. Current Mode                         | 46        |

| 3.5  | Conclusion                                                  | 47        |

| Chap | ter 4 LED Driver Circuit Architecture Design Enabling Con-  |           |

| cu   | rrent Data Transmission and Dimming Control for VLC         | <b>49</b> |

| 4.1  | Intoduction                                                 | 49        |

| 4.2  | Commercial LED Driver's Conflict with VLC                   | 50        |

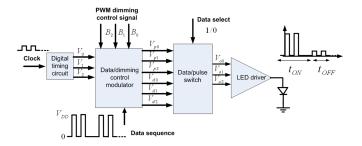

| 4.3  | A Digitally-controlled, Bi-level CMOS LED Driver Circuit    | 52        |

|      | 4.3.1 Analysis and Design of LED Driver Architecture        | 53        |

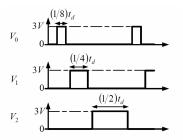

|      | 4.3.2 Digital Timing Circuit                                | 54        |

|      | 4.3.3 Data/Dimming Control Modulator                        | 55        |

|      | 4.3.4 Simulation Results of Digitally-Controlled LED Driver | 57        |

| 4.4  | LED Driver Circuit Architecture Utilizing Analog Dimming    | 60        |

|        | 4.4.1  | Introduction                                              | 60  |

|--------|--------|-----------------------------------------------------------|-----|

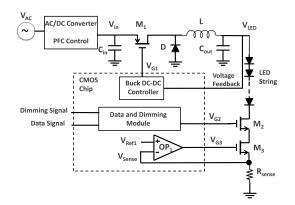

|        | 4.4.2  | Buck Converter Design                                     | 62  |

|        | 4.4.3  | Data-Dimming Multiplication Method                        | 65  |

|        | 4.4.4  | High Gain-Bandwidth and High Slew-Rate Two-Stage OTA .    | 66  |

|        | 4.4.5  | Measurement Results of LED Driver with Analog Dimming .   | 73  |

| 4.5    | Concl  | usion                                                     | 79  |

| Chapte | er 5 I | Bandwidth Enhancement Techniques for VLC Networks         | 80  |

| 5.1    | Introd | luction                                                   | 80  |

| 5.2    | Negat  | ive Impedance Converter (NIC)                             | 83  |

|        | 5.2.1  | Accurate Formula for NIC                                  | 85  |

|        | 5.2.2  | Proposed LED Driver Based on the Floating Negative Capac- |     |

|        |        | itance                                                    | 88  |

|        | 5.2.3  | Proposed LED Driver using Fixed Negative C Circuit        | 90  |

| 5.3    | Equal  | ization and Complex Modulations                           | 91  |

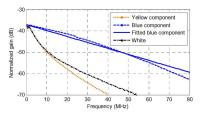

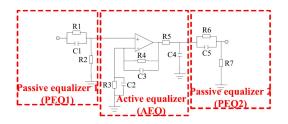

|        | 5.3.1  | Multiple-Resonant Equalization                            | 92  |

|        | 5.3.2  | Passive Equalization at the Receiver                      | 93  |

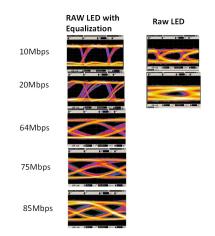

|        | 5.3.3  | Active-Passive Equalization at the Receiver               | 96  |

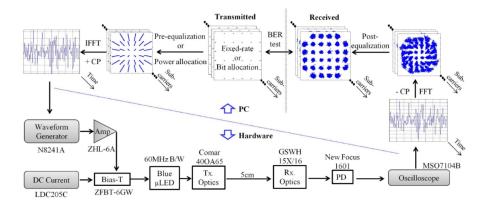

|        | 5.3.4  | Using Complex Modulation: DMT and OFDM $\ . \ . \ . \ .$  | 97  |

| 5.4    | Bandy  | width Enhancement using Pulse Shaping                     | 99  |

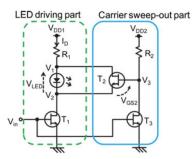

|        | 5.4.1  | Carrier Sweep-out                                         | 100 |

|        | 5.4.2  | Pulse Shaping Circuit                                     | 101 |

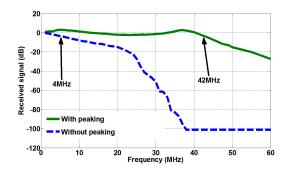

| 5.5    | Bandy  | width Enhancement with Peaking                            | 104 |

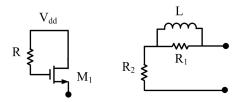

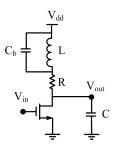

|        | 5.5.1  | Shunt Peaking                                             | 104 |

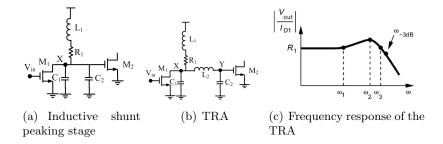

|        | 5.5.2  | Active Inductive Shunt Peaking                            | 106 |

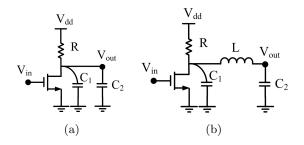

|        | 5.5.3  | Bridged-Shunt Peaking                                     | 106 |

|        | 5.5.4  | Series Peaking                                            | 107 |

|        | 5.5.5  | Triple-Resonance Architecture                             | 108 |

|        | 5.5.6  | Bridged-Shunt-Series Peaking                              | 109 |

|        | 5.5.7  | Proposed Bridged-Shunt-Zero Peaking                       | 111 |

| 5.6     | Bandwidth Extension by Pole Zero Cancellation 116              |     |  |

|---------|----------------------------------------------------------------|-----|--|

| 5.7     | Bandwidth Extension using Time Interleaved LEDs                | 119 |  |

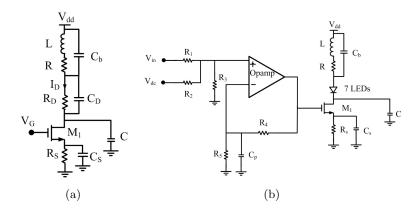

|         | 5.7.1 Transmitter Design using Time Interleaved LEDs           | 122 |  |

| 5.8     | 16-Level Pulse Amplitude Modulation of an LED Array            | 125 |  |

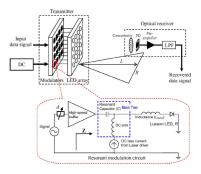

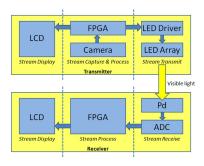

|         | 5.8.1 VLC System Description for PAM Implementation            | 126 |  |

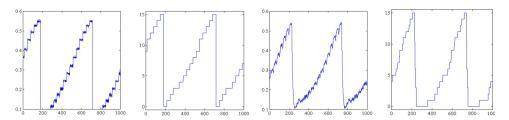

|         | 5.8.2 Experimental Results for 16-Level PAM                    | 129 |  |

| 5.9     | Conclusion                                                     | 130 |  |

| Chapte  | er 6 Demonstrations                                            | 132 |  |

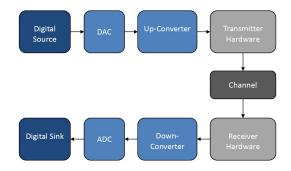

| 6.1     | Implementation using Software Defined Radio (SDR)              | 132 |  |

|         | 6.1.1 SDVLC Hardware Architecture                              | 133 |  |

|         | 6.1.2 Additional Applications                                  | 140 |  |

| 6.2     | Wireless Access Testbed through Visible Light and Dimming Com- |     |  |

|         | patible OFDM                                                   | 141 |  |

|         | 6.2.1 Introduction                                             | 141 |  |

|         | 6.2.2 Dimming and Modulation in VLC                            | 143 |  |

|         | 6.2.3 PCB Based Luminaire                                      | 145 |  |

|         | 6.2.4 Measurement Results                                      | 148 |  |

| 6.3     | Conclusion                                                     | 151 |  |

| Classi  |                                                                | 150 |  |

| Chapte  | er 7 Conclusion and Future Work                                | 153 |  |

| Bibliog | graphy                                                         | 157 |  |

|         |                                                                |     |  |

# List of Tables

| 2.1 | Photometric and corresponding radiometric units           | 10  |

|-----|-----------------------------------------------------------|-----|

| 2.2 | Summary of photometric performance measures for LEDs      | 12  |

| 2.3 | Semiconductor materials and emission wavelengths $\hdots$ | 16  |

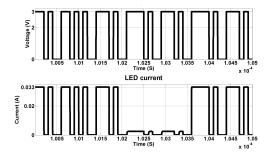

| 4.1 | Summary of proposed design                                | 59  |

| 4.2 | LED average current in different schemes                  | 59  |

| 4.3 | Performance summary comparison of different OTAs          | 74  |

| 4.4 | Chip and buck converter perfomance                        | 78  |

| 5.1 | Performance metrics for shunt peaking                     | 105 |

| 5.2 | Performance metrics for series peaking                    | 108 |

| 5.3 | Bridged-shunt-series peaking summary                      | 110 |

# List of Figures

| 2.1  | Luminous efficiency of LEDs and other sources vs. time                                   | 9  |

|------|------------------------------------------------------------------------------------------|----|

| 2.2  | Area of LED, A, and projected area, A $\cos\Theta$ used for the definition               |    |

|      | of the luminance of an LED                                                               | 10 |

| 2.3  | Relation of maximum possible luminous efficacy and chromaticity                          | 11 |

| 2.4  | Horizontal illuminance of LED                                                            | 13 |

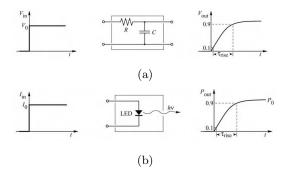

| 2.5  | (a) Illustration of a linear RC system response, (b) Illustration of                     |    |

|      | light output power                                                                       | 18 |

| 2.6  | Equivalent circuit of a forward biased LED                                               | 21 |

| 2.7  | The diode equivalent circuit                                                             | 24 |

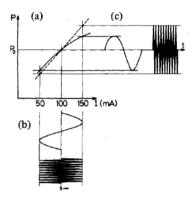

| 2.8  | Low-frequency response (a) Power vs. current (b) Current signal (c)                      |    |

|      | Modulated optical signal                                                                 | 28 |

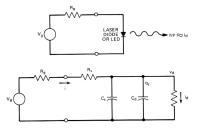

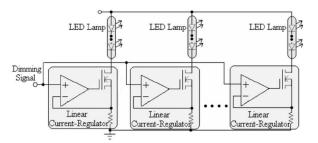

| 3.1  | Conventional amplitude-mode driving                                                      | 32 |

| 3.2  | Conventional linear current-regulator method for multiple LEDs $~$                       | 33 |

| 3.3  | Conventional PWM-mode driving                                                            | 33 |

| 3.4  | Conventional PWM-mode driving technique using multiple LEDs $\ . \ .$                    | 34 |

| 3.5  | The LED current and voltage waveforms of bilevel current driving $% \mathcal{L}^{(1)}$ . | 36 |

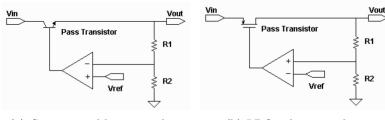

| 3.6  | Linear voltage regulator topologies                                                      | 37 |

| 3.7  | AC pole locations without compensation                                                   | 37 |

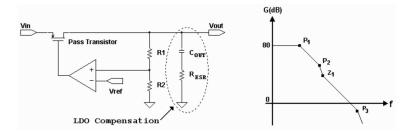

| 3.8  | Conventional LDO regulator compensation                                                  | 38 |

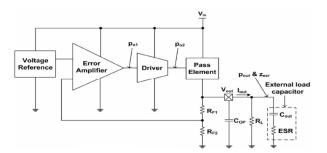

| 3.9  | Internal block diagram of a conventinal LDO                                              | 39 |

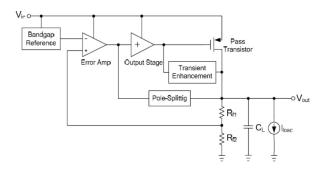

| 3.10 | LDO with enhancement transient response                                                  | 41 |

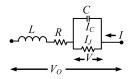

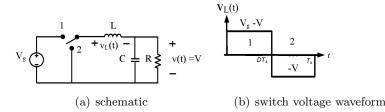

| 3.11 | The buck converter consists of a switch network and a low-pass filter         | 42 |

|------|-------------------------------------------------------------------------------|----|

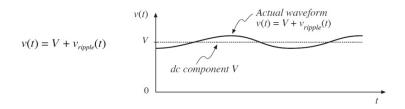

| 3.12 | Realization of the ideal switch using a transistor and free<br>wheeling diode | 43 |

| 3.13 | Small ripple approximation                                                    | 44 |

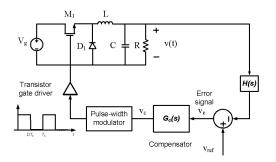

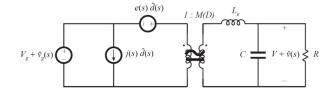

| 3.14 | The canonical model for DC-DC converters                                      | 46 |

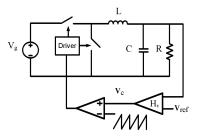

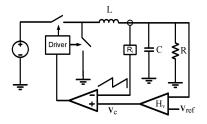

| 3.15 | Voltage-mode control structure                                                | 47 |

| 3.16 | Current-mode control structure                                                | 47 |

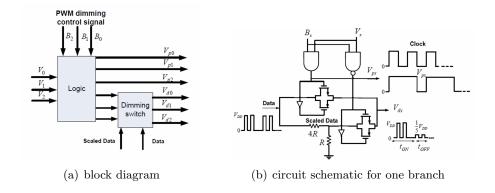

| 4.1  | A digitally-controlled LED driver circuit block diagram                       | 53 |

| 4.2  | Output waveforms of the digital timing circuit                                | 55 |

| 4.3  | Data/dimming control modulator circuit                                        | 56 |

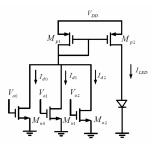

| 4.4  | Analog circuit schematic of digitally-controlled LED driver                   | 57 |

| 4.5  | LED electrical model                                                          | 57 |

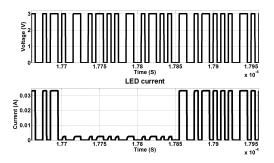

| 4.6  | LED current waveform for NRZ data modulation                                  | 58 |

| 4.7  | LED current waveform for RZ data modulation                                   | 58 |

| 4.8  | LED current waveform for Manchester coding                                    | 58 |

| 4.9  | LED current with no data                                                      | 58 |

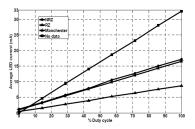

| 4.10 | Average LED current versus duty cycle                                         | 60 |

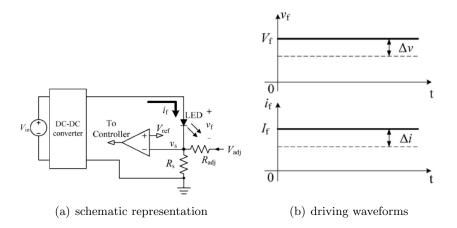

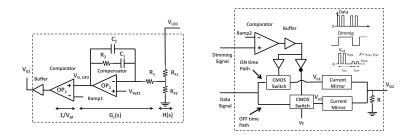

| 4.11 | Block diagram of LED driver utilizing analog dimming                          | 61 |

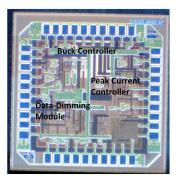

| 4.12 | Chip block diagrams and its micrograph                                        | 64 |

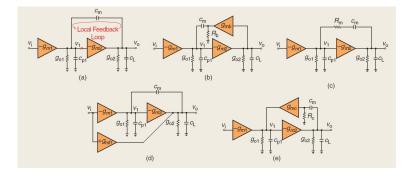

| 4.13 | Compensation schemes for two stage OpAmps: (a) Simple Miller                  |    |

|      | compensation (SMC), (b) Miller compensation with voltage buffer               |    |

|      | (MCVB), (c) Miller compensation with nulling resistor (MCNR), (d)             |    |

|      | Miller compensation with feedforward transconductance (MCFT),                 |    |

|      | and (e) Miller compensation with current buffer (MCCB).                       | 68 |

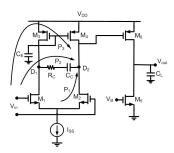

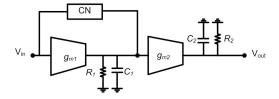

| 4.14 | Circuit diagram of OTA with its proposed compensation method                  | 70 |

| 4.15 | Block diagram of OTA with two distinct compensation networks $\ . \ .$        | 71 |

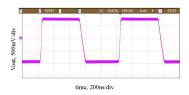

| 4.16 | Experimental transient response with 15pF load                                | 72 |

| 4.17 | Open-loop frequency response simulation results                               | 72 |

| 4.18 | Chip microphotograph of the two-stage OTA                                     | 73 |

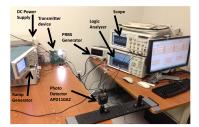

| 4.19 | Measurement setup developed for optical characterization of the LED                                            |     |

|------|----------------------------------------------------------------------------------------------------------------|-----|

|      | driver circuit                                                                                                 | 74  |

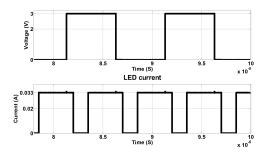

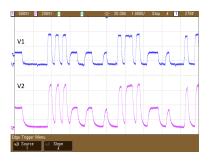

| 4.20 | Transient analysis of the LED driver chip and its zoomed in view                                               |     |

|      | of transient signals with $2^7 - 1$ PRBS, NRZ modulated data signal                                            |     |

|      | and %30 dimming level. V1: is Vo1 in Figure 4.12(b), V2: is $V_{o2}$ in                                        |     |

|      | Figure 4.12(b), $V3$ : is Vsense in Figure 4.11 which is proportional to                                       |     |

|      | LED current, and V4: is the received signal using the $APD110A2$                                               |     |

|      | commercial receiver                                                                                            | 75  |

| 4.21 | Measurement result at the link range of $50cm$ and dimming level of                                            |     |

|      | 60%, V1: $V_{sense}$ in Figure 4.11 which is proportional to LED current,                                      |     |

|      | and V2: Output of commercial receiver, $APD110A2$                                                              | 75  |

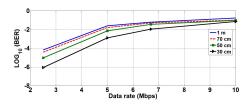

| 4.22 | BER vs data rate for different link ranges                                                                     | 76  |

| 4.23 | Variation of BER versus dimming ratio for 5Mbps data rate ( $R$ : ratio                                        |     |

|      | of on-time to off-time of PWM signal), (a) Link range of $100cm$ , (b)                                         |     |

|      | Link range of $70cm$ , (c) Link range of $50cm$ , (d) Link range of $30cm$                                     | 76  |

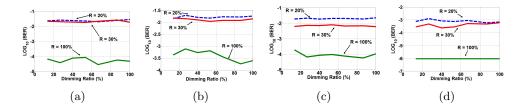

| 4.24 | Eye diagrams: (a) Data rate of 5Mbps, link range of $50cm$ , (b) Data                                          |     |

|      | rate of 5Mbps, link range of $1m$ , (c) Data rate of 10Mbps, link range                                        |     |

|      | of 50 <i>cm</i> , and (d) Data rate of 10Mbps, link range of $1m$                                              | 77  |

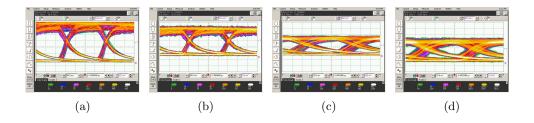

| 4.25 | Lux measurements: (a) Lux versus data rate (b) Lux versus the dim-                                             |     |

|      | ming ratio for different dara-rates at $30cm$ of link range $\ldots$ $\ldots$                                  | 77  |

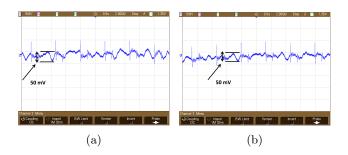

| 4.26 | Output voltage ripple: (a) $30\%$ dimming level, (b) $70\%$ dimming level                                      | 78  |

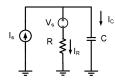

| 5.1  | Simplified model of LED driven by a current $I_s$                                                              | 83  |

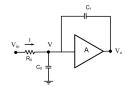

| 5.2  | Negative capacitance bus terminator $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                         | 83  |

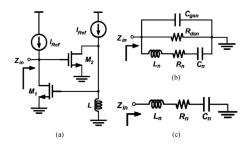

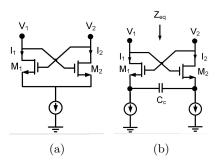

| 5.3  | Negative capacitance cell: (a) Simplified circuit schematic, (b) Small                                         | 00  |

| 0.0  | signal equivalent circuit, (c) Simplified equivalent circuit                                                   | 84  |

| 5.4  | Circuit schematic of (a) Floating negative resistor, and (b) Floating                                          | 04  |

| 5.4  |                                                                                                                | or  |

|      | negative capacitance $\ldots$ | 85  |

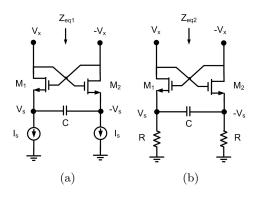

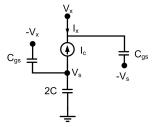

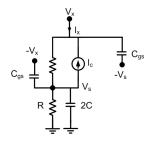

| 5.5  | Calculating the accurate value of the floating negative $C$ (a) Using                                          | 0.0 |

|      | current source, (b) Using resistor $R$                                                                         | 86  |

| 5.6                                                                                                                                      | Equivalent of circuit shown in Figure 5.5(a) $\ldots \ldots \ldots \ldots \ldots$                                                                                                 | 86                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| 5.7                                                                                                                                      | Equivalent of circuit shown in Figure 5.5(b) $\ldots \ldots \ldots \ldots \ldots$                                                                                                 | 87                                                                                                    |

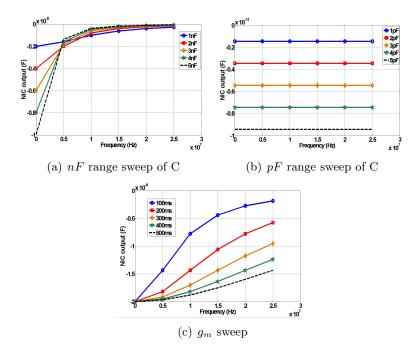

| 5.8                                                                                                                                      | The sweep of $C$ and $g_m$ of floating NIC $\ldots \ldots \ldots$ | 88                                                                                                    |

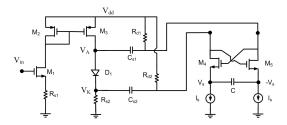

| 5.9                                                                                                                                      | The proposed LED driver with floating negative $C$ circuit $\ldots$ .                                                                                                             | 89                                                                                                    |

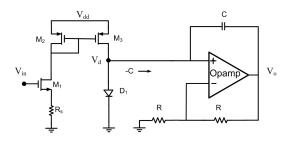

| 5.10                                                                                                                                     | Frequency response of the circuit shown in Figure 5.9                                                                                                                             | 89                                                                                                    |

| 5.11                                                                                                                                     | Schematic of the proposed LED driver utilizing the fixed negative ${\cal C}$                                                                                                      | 90                                                                                                    |

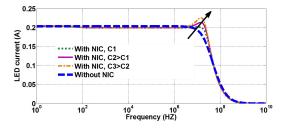

| 5.12                                                                                                                                     | Frequency response of the proposed circuit shown in Figure 5.11 $$                                                                                                                | 91                                                                                                    |

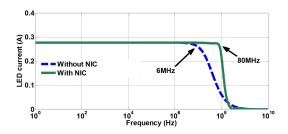

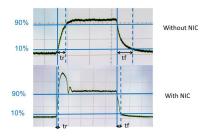

| 5.13                                                                                                                                     | Measurement result for rise and fall time with and without using NIC                                                                                                              | 91                                                                                                    |

| 5.14                                                                                                                                     | VLC testbed system using an array of 16 resonated white LEDs                                                                                                                      | 93                                                                                                    |

| 5.15                                                                                                                                     | VLC system with post-equalizer                                                                                                                                                    | 93                                                                                                    |

| 5.16                                                                                                                                     | Modulation bandwidths of individual components                                                                                                                                    | 94                                                                                                    |

| 5.17                                                                                                                                     | Measurement results of first order equalization in the receive side                                                                                                               | 96                                                                                                    |

| 5.18                                                                                                                                     | VLC post-equalization circuit using passive and active components .                                                                                                               | 97                                                                                                    |

| 5.19                                                                                                                                     | Experimental setup of single LED OFDM based wireless VLC link $% \mathcal{A} = \mathcal{A} = \mathcal{A}$ .                                                                       | 98                                                                                                    |

| 5.20                                                                                                                                     | Schematic of LED driver for sweeping out the carriers using discrete                                                                                                              |                                                                                                       |

| 0.20                                                                                                                                     |                                                                                                                                                                                   |                                                                                                       |

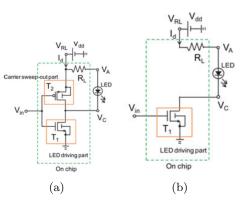

| 0.20                                                                                                                                     | GaAs FETs                                                                                                                                                                         | 101                                                                                                   |

|                                                                                                                                          |                                                                                                                                                                                   | 101                                                                                                   |

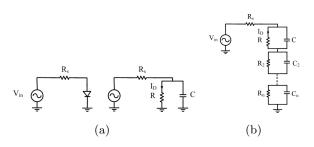

|                                                                                                                                          | GaAs FETs                                                                                                                                                                         | 101<br>101                                                                                            |

| 5.21                                                                                                                                     | GaAs FETs                                                                                                                                                                         |                                                                                                       |

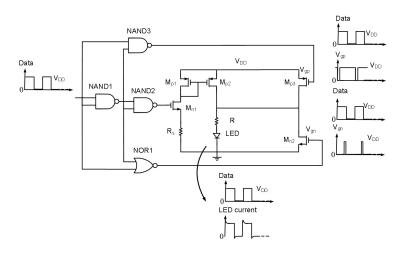

| 5.21<br>5.22                                                                                                                             | GaAs FETs                                                                                                                                                                         | 101                                                                                                   |

| <ul><li>5.21</li><li>5.22</li><li>5.23</li></ul>                                                                                         | GaAs FETs                                                                                                                                                                         | 101<br>102                                                                                            |

| <ul><li>5.21</li><li>5.22</li><li>5.23</li></ul>                                                                                         | GaAs FETs                                                                                                                                                                         | 101<br>102                                                                                            |

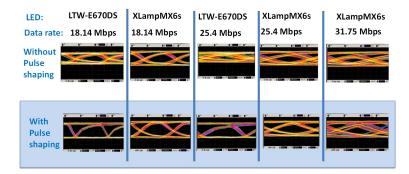

| <ul><li>5.21</li><li>5.22</li><li>5.23</li><li>5.24</li></ul>                                                                            | GaAs FETs                                                                                                                                                                         | 101<br>102<br>103                                                                                     |

| <ul> <li>5.21</li> <li>5.22</li> <li>5.23</li> <li>5.24</li> <li>5.25</li> </ul>                                                         | GaAs FETs                                                                                                                                                                         | 101<br>102<br>103<br>105                                                                              |

| <ul> <li>5.21</li> <li>5.22</li> <li>5.23</li> <li>5.24</li> <li>5.25</li> <li>5.26</li> </ul>                                           | GaAs FETs                                                                                                                                                                         | 101<br>102<br>103<br>105<br>106                                                                       |

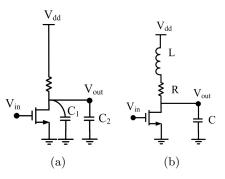

| <ul> <li>5.21</li> <li>5.22</li> <li>5.23</li> <li>5.24</li> <li>5.25</li> <li>5.26</li> <li>5.27</li> </ul>                             | GaAs FETs                                                                                                                                                                         | <ol> <li>101</li> <li>102</li> <li>103</li> <li>105</li> <li>106</li> <li>106</li> </ol>              |

| <ol> <li>5.21</li> <li>5.22</li> <li>5.23</li> <li>5.24</li> <li>5.25</li> <li>5.26</li> <li>5.27</li> <li>5.28</li> </ol>               | GaAs FETs                                                                                                                                                                         | 101<br>102<br>103<br>105<br>106<br>106<br>107                                                         |

| <ol> <li>5.21</li> <li>5.22</li> <li>5.23</li> <li>5.24</li> <li>5.25</li> <li>5.26</li> <li>5.27</li> <li>5.28</li> </ol>               | GaAs FETs                                                                                                                                                                         | <ol> <li>101</li> <li>102</li> <li>103</li> <li>105</li> <li>106</li> <li>106</li> <li>107</li> </ol> |

| <ol> <li>5.21</li> <li>5.22</li> <li>5.23</li> <li>5.24</li> <li>5.25</li> <li>5.26</li> <li>5.27</li> <li>5.28</li> <li>5.29</li> </ol> | GaAs FETs                                                                                                                                                                         | 101<br>102<br>103<br>105<br>106<br>106<br>107<br>108                                                  |

| 5.31 | Modified bridged-shunt peaking                                                                                                                                                                        | 111 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.32 | Source degeneration and its frequency response                                                                                                                                                        | 112 |

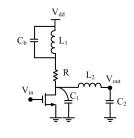

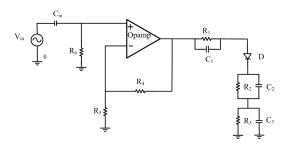

| 5.33 | Proposed LED driver circuit using bridged-shunt-zero peaking                                                                                                                                          | 113 |

| 5.34 | Inductor-less bridged shunt-zero peaking circuit                                                                                                                                                      | 114 |

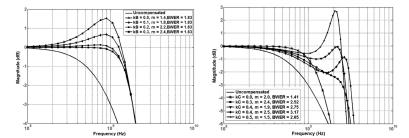

| 5.35 | Frequency response of the proposed bridged-shunt-zero peaking                                                                                                                                         | 116 |

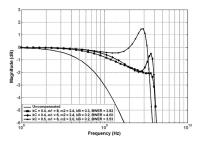

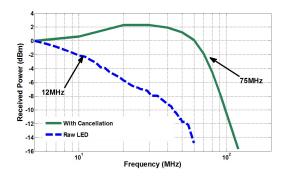

| 5.36 | LED drives with pole zero cancellation                                                                                                                                                                | 116 |

| 5.37 | Proposed LED driver with pole-zero cancellation technique                                                                                                                                             | 118 |

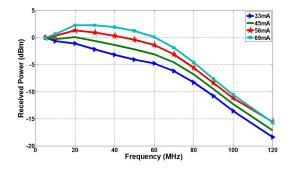

| 5.38 | The frequency response with and without using pole-zero cancellation                                                                                                                                  | 119 |

| 5.39 | Frequency response comparison for different LED currents                                                                                                                                              | 119 |

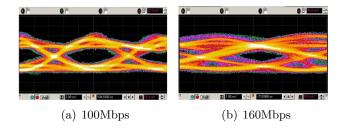

| 5.40 | Measured eye diagram of the proposed pole-zero cancellation tech-                                                                                                                                     |     |

|      | nique                                                                                                                                                                                                 | 120 |

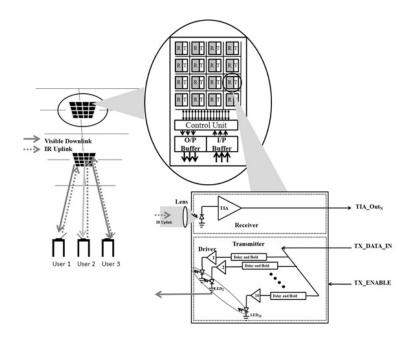

| 5.41 | Conceptual diagram of the Smart Room with the proposed optical                                                                                                                                        |     |

|      | access point transceiver block diagram                                                                                                                                                                | 121 |

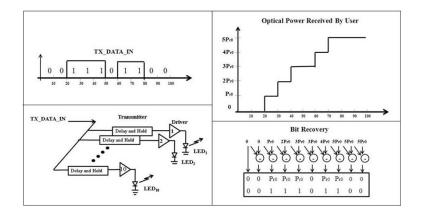

| 5.42 | Time interleaved data coding based 100Mbps transmission scheme $% \left( {{{\left( {{{\left( {{{\left( {{{\left( {{{c}}} \right)}} \right.} \right.} \right)}_{0.00000000000000000000000000000000000$ | 122 |

| 5.43 | LED driver with current regulation                                                                                                                                                                    | 124 |

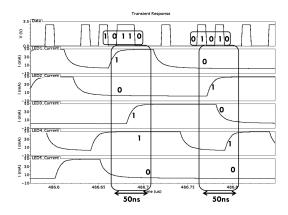

| 5.44 | Transient simulation of the LED transmitter with a PRBS source                                                                                                                                        | 125 |

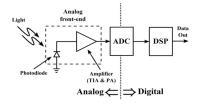

| 5.45 | VLC system block diagram for PAM implementation                                                                                                                                                       | 126 |

| 5.46 | OOK versus pulse amplitude modulation                                                                                                                                                                 | 127 |

| 5.47 | LED driver PCB for 16-level PAM                                                                                                                                                                       | 128 |

| 5.48 | Raw restored data after PD versus modified restored data after soft-                                                                                                                                  |     |

|      | ware processing procedure                                                                                                                                                                             | 130 |

| 6.1  | High level signal chain for a software defined communication link $\ .$ .                                                                                                                             | 134 |

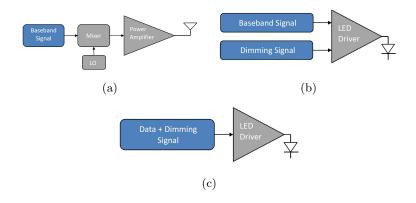

| 6.2  | (a) Signal chains for an SDR transmitter, (b) an SDVLC transmitter                                                                                                                                    |     |

|      | with dimming and data as separate inputs, (c) an SDVLC transmitter                                                                                                                                    |     |

|      | with a single input with combined data and dimming signal                                                                                                                                             | 134 |

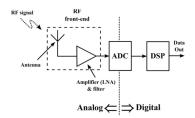

| 6.3  | SDR RF receiver front-end                                                                                                                                                                             | 136 |

| 6.4  | SDVLC optical receiver front-end                                                                                                                                                                      | 136 |

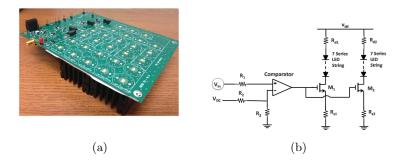

| 6.5  | First analog LED driver for SDR demonstration: (a) LED driver                                                                                                                                         |     |

|      | PCB, (b) LED driver circuit                                                                                                                                                                           | 137 |

| 6.6  | Second analog LED driver for SDR demonstration: (a) Two-level                          |     |

|------|----------------------------------------------------------------------------------------|-----|

|      | LED driver PCB, (b) Two-level LED driver circuit                                       | 138 |

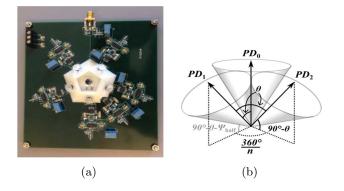

| 6.7  | Receiver: (a) Diversity receiver PCB, (b) FOV design model for an                      |     |

|      | arbitrary $n$                                                                          | 139 |

| 6.8  | Software defined VLC implementation                                                    | 140 |

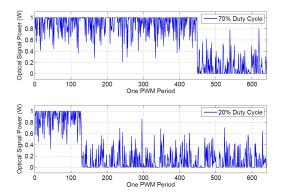

| 6.9  | Optical RPO-OFDM signal waveform based on ACO-OFDM at $70\%$                           |     |

|      | (upper) and 20% (lower) duty-cycles $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 145 |

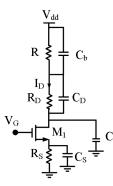

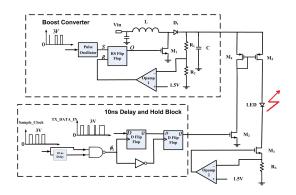

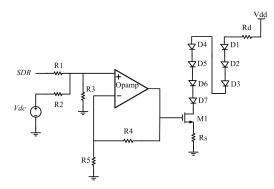

| 6.10 | The schematic diagram of proposed LED driver for dimming compat-                       |     |

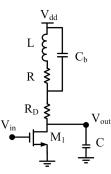

|      | ible OFDM                                                                              | 146 |

| 6.11 | The PCB luminaire for dimming compatible OFDM                                          | 147 |

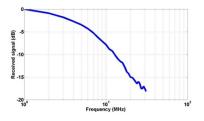

| 6.12 | The frequency response of LED driver                                                   | 148 |

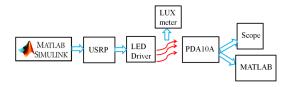

| 6.13 | Block diagram of the testbed                                                           | 149 |

| 6.14 | The measurement setup for dimming compatible OFDM                                      | 149 |

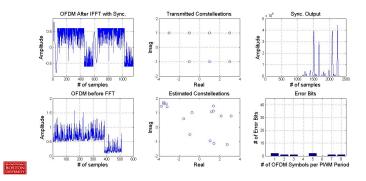

| 6.15 | The MATLAB GUI showing the generated RPO-OFDM signal (us-                              |     |

|      | ing 8-QAM) (upper left), the ideal QAM constellations (upper mid-                      |     |

|      | dle), the peaks of the correlation process to realize frame synchro-                   |     |

|      | nization (upper right), the received RPO-OFDM after extracting the                     |     |

|      | RPO-OFDM from the PWM signal (lower left), the estimated con-                          |     |

|      | stellations (lower middle) and the number of bits in error per OFDM                    |     |

|      | symbol where 8 symbols are used within a PWM period (lower right)                      | 150 |

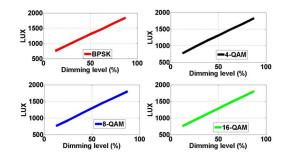

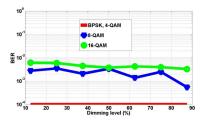

| 6.16 | Linear change of dimming for different modulation schemes $\ldots$ .                   | 151 |

| 6.17 | BER vs dimming level for different modulation schemes. Error free                      |     |

|      | BER is obtained for BPSK and 4-QAM                                                     | 151 |

# Chapter 1

# Introduction

### 1.1 Motivation

Electrical lighting has revolutionized society over the last century, and today electrical lighting is on the verge of yet another revolution. Energy bills legislation, introduced in 2007 by Congress, has banned the use of incandescent light bulb by the year 2014 [1]. With the development of semiconductor-based light generated by light-emitting diodes (LEDs), the second generation of lighting known as solid state lighting (SSL) has been shown to provide greater energy efficiency compared to the conventional incandescent light bulb. SSL technology has shown great promise in providing multiple benefits such as improved health and safety to the society, energy efficiency, and improved productivity. This lighting technology evolution has not only proven to be a suitable replacement for incandescent light bulbs, but has also provided enhancements in each beneficial area while establishing the prominent core competencies for this new age of lighting. The full potential of SSL technology, however, has not yet been fully achieved. The SSL technologys vision has been to ultimately attain the full potential of light by capitalizing on energy efficiency and improve sustainability.

The white LED stands at the threshold of a new era of energy-efficient lighting bringing revolutionary advances in the use of light for illumination and a host of other applications, including sensing, navigation, and communications.

With the increasing global demand for anywhere, anytime connectivity to mobile devices, there is a growing need to develop wireless access technologies that are broadband, interference-resistant, reliable, and cost-effective [2]. The major step towards the vision of ubiquitous wireless connectivity and the development of green, environmentally-friendly wireless networks is using white LEDs. We have witnessed the tremendous capacity provided by optical signals in telecommunications networks and the emergence of the white LED presents an opportunity to extend the reach of optical signals in free-space. This vision leads to a special case of optical wireless which is called visible light communication (VLC), where an additional advantage lies in simultaneous use of light sources as illumination and communication. The realization of visible light networks combining both illumination control and high-speed wireless connectivity to computers, peripheral components, and mobile devices presents a number of new challenges at all levels of system development. One of the grand challenges is bidirectional/uplink transmission in a visible light network. Hybrid RF/LED program considers the growing interest in hybrid communication systems as a viable system topology for indoor visible light communication [3]. A hybrid system combines the advantages of unlimited bandwidth free - space optical (FSO) signaling and high mobility RF wireless transmission to extend the bandwidth, reduce power consumption, lower cost, and provide high adaptability to dynamic operational environment. For indoor visible light communication, a combined hybrid RF/LED link improves reliability and bit error rate performance; and provides greater immunity to blocking. To capitalize on large - scale energy savings of solid-state lighting, hybrid system realization requires advanced integration and packaging techniques that take advantage of low cost, commodity silicon micro-fabrication processing (CMOS) which has been advanced over the past decades. Furthermore, novel approaches to device integration are necessary to account for several order dimensional discrepancy between antenna geometries measured in millimeters at microwaves and typical submillimeter dimensions of active optical components.

Here we have presented the concurrent combination of data signals with

dimming control signals. Two methods of digital and analog generation of PWM signals and its combination with data signals in  $0.5\mu m$  and 180nm CMOS technology are developed, respectively. The main challenge of implementing a fast link in VLC networks is emanated from the inherent bandwidth limitations of LEDs. The typical 3dB frequency bandwidth of white LEDs is in the range of 5-12MHz. To alleviate this challenge a number of bandwidth enhancement techniques are proposed, designed, and manufactured. The first one is called negative impedance converter (NIC) which generates a negative capacitance used to cancel out the parasitic capacitance of LED and hence increase the overall bandwidth. Then different equalization methods are reviewed and pulse shaping circuit which increases the bandwidth by shaping the LED current signal to have smaller rise and fall times is presented. The other method is the high speed design using peaking and equalization techniques where it enhances the overall bandwidth by generating peaking in the frequency response. The next method covered here is the pole-zero cancellation and can be applied to both digital and analog modulation techniques. After that, the time interleaved technique is introduced which is a mechanism of sending data with some fixed delays in order to increase the total number of bits per second. Finally, the pulse amplitude modulation which uses 16-level resolution is presented; 16-level PAM is capable of increasing the data rate by four times.

### **1.2** Thesis Organization

Chapter 2 provides an introduction to the visible light communication networks, and its analysis. It also takes a look at the LED as a source and discuss its transient and frequency behavior.

Chapter 3 focuses on the conventional LED driver circuit architectures. Amplitude and PWM driving modes are reviewed and then Linear as well as the switching regulators for implementing in LED drivers are discussed in this chapter.

Chapter 4 presents a novel LED driver circuit architecture design enabling concurrent data transmission and dimming control for VLC. It introduces a digitallycontrolled bi-level LED driver analysis and design. In addition, it introduces the digital combination of data signals with dimming controls generated using the analog dimming signal. It also contains the discussion of design and implementation of a novel two-stage OTA designed to be used in the feedback loop control of the LED driver.

Chapter 5 covers novel and distinct types of bandwidth enhancement techniques which composed of negative impedance converter, high speed design using equalization, pulse shaping circuit, peaking, pole-zero cancellation, time interleaved LEDs, and 16-level pulse amplitude modulation.

Chapter 6 presents the experimental demonstrations developed to prove the concept of the VLC system design. The transmission of digital signals using the software defined rasio (SDR) setup, and transmission of OFDM analog signals using the MATLAB/Simulink setup are explained in this chapter.

Chapter 7 summarizes and concludes the contribution of this thesis. Future work that would further enhance the bandwidth of the system are also suggested.

# Chapter 2

# Visible Light Communication using White LEDs

### 2.1 Introduction

LED is more advantageous than the existing light sources like incandescent in terms of long life expectancy, high tolerance to humidity, low power consumption, and minimal heat generation lighting. White light can be generated by mixing three primary colors of red, green and blue. The other way is combination of blue LED with the coating of phosphorus. This white LED is considered as a strong candidate for the future lighting technology. Compared with conventional lighting methods, white LED has lower power consumption and lower voltage, longer lifetime, smaller size, and cooler operation. Even though the LED entitles the aforementioned features, this device put some restrictions in terms of its inherent bandwidth. LED devices have inherent bandwidth limitations which limit data transmission speeds in future visible light communication networks. In this chapter first we review the VLC system and its analysis. And then the LEDs, which are going to be used in this VLC system for translating the modulation and illumination control signals into the light are reviewed in terms of its transient and frequency response.

### 2.2 Visible Light Communication (VLC)

Visible light communications (VLC) is the latest optical wireless communications technologies that uses low-power light emitting diodes, or LEDs, not only to provide light but also to broadcast data. LEDs are extremely energy-efficient and predicted to become widespread in general lighting application. Because LED is a solid-state lighting device, it can be modulated at high-speed compared with other lighting sources. VLC uses LEDs, which send data by flashing light at speeds undetectable to the human eye. It is expected that LED market will reach \$29 billion in 2017 that is comparable to today's NAND and DRAM markets [4]. The pioneer of VLC using LEDs is Professor Masao Nakagawa of Keio University. His first paper on this subject appeared in the early 2000, together with his successor Prof. Shinichiro Haruyama [5]. Later in 2003, he formed Visible Light Communication Consortium (VLCC).

Widespread use of LEDs in traffic applications and growing interest in intelligent transport system (ITS) presents an opportunity for VLC. In 2006 Siemens launched VLC project. Later in 2008, European Commission established OMEGA project with a consortium of 20 European partners from industry and the scientific community. Meanwhile, in 2008, the US national science foundation (NSF) has approved a grant of \$18.5 million to help establish and the engineering research center (ERC) focuses on VLC. The members of the center include the Rensselaer Polytechnic Institute (RPI), Boston University (BU) and the University of New Mexico (UNM). The University of California also have launched five-year research project starting from 2009, called the Ubiquitous Communication by Light (UC-Light) that is founded with \$3.5 million from the University [4]. VLC is in the process of standardization by the IEEE 802.15 TG7 and VLCC as well as other standard organizations.

The IEEE 802.15.7 standard was approved to define PHY and MAC layer protocols for short-range free-space optical communication using visible light. As a result of concurrent illumination control and data transmission within a visible

light network, luminaires will be able to wirelessly communicate with each other and coordinate their appropriate functionality. The light will also be able to deliver data to mobile users, without relying on increasingly congested radio frequency (RF) wireless channels. Recent advancements in biochemical sensing, will enable the network to monitor biohazardous materials, and when appropriate, destroy the biohazards by activating deep ultra-violet (UV) LEDs. Moreover, even with these advanced capabilities, the VLCs smart lighting has substantiated its utilization to be more energy-efficient than current lighting systems by combining more efficient, properly designed, color-tunable LED systems with advanced adaptive control networks. The energy conserved from smart lighting, according to the electrical energy savings forecast by the department of energy (DOE), will be doubled by the use of white LED systems. The additional electrical energy savings is roughly equivalent to the elimination of over 300 coal-fired power plants accompanied by large reduction in greenhouse gas emissions. VLC offers several potential advantages over RF communications. It can provide more secure communications over a shorter range because walls and curtains can easily block light signals, whereas potential eavesdroppers can easily detect RF signals from outside buildings. The technology could be useful in factories and hospitals, in which radio transmissions are either impossible or limited owing to concerns about RF interference with critical equipment. The new technology's main limitation is that it is primarily envisioned as one-way broadcast technology. Bidirectional communications would have to occur over a different technology such as Wi-Fi. Several efforts are under way to develop VLC standards. In the next section the analysis of VLC system is described.

### 2.3 Fundamental Analysis for VLC

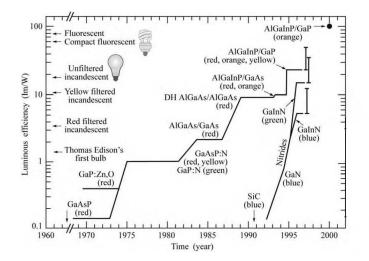

The advancement of LED efficiency can be compared to the advancement made in silicon integrated circuits where the performance increase versus time has been characterized by Moore's law which states that the performance of silicon integrated circuits doubles approximately every 18 months. The historical development of the luminous efficiency of visible-spectrum LEDs is shown in Figure 2.1 [6]. The chart illustrates the modest beginnings of visible-spectrum LED technology which started in the 1960s. If the progress from 1960 to 2000 is assumed to be continuous, then the LED luminous efficiency has doubled every 4 years. In order to introduce the VLC analysis, it is needed to have a better understanding of the photometric units used to characterize the light intensity. The definitions and descriptions of the system in this regard is summarized in the following sections [6].

#### 2.3.1 Basic Photometric Units

The physical properties of electromagnetic radiation are characterized by radiometric units. Using radiometric units, we can characterize light in terms of physical quantities; for example, the number of photons, photon energy, and optical power. However, the radiometric units are irrelevant when it comes to light perception by a human being. For example, infrared radiation causes no luminous sensation in the eye. To characterize the light and color sensation by the human eye, different types of units, called photometric units, are needed.

#### 2.3.1.1 Luminous Flux, Luminous Intensity, and Illuminance

Although the term brightness is frequently used, it lacks a standardized scientific definition. The frequent usage is due to the fact that the general public can more easily relate to the term brightness than to photometric terms such as luminance or luminous intensity [6].

The luminous flux represents the light power of a source as perceived by the human eye. The unit of luminous flux is lumen (lm), which is defined in international system of units (SI unit).

The luminous flux,  $\Phi_{lum}$ , is obtained from the radiometric light power using the Equation (2.1).

$$\Phi_{lum} = 683 \frac{lm}{W} \int_{\lambda} V(\lambda) P(\lambda) d\lambda$$

(2.1)

Figure 2.1: Luminous efficiency of LEDs and other sources vs. time

where  $V(\lambda)$  is luminous efficiency function or eye sensitivity function,  $P(\lambda)$  is the power spectral density, *i.e.* the light power emitted per unit wavelength, and the prefactor 683 lm/W is a normalization factor.

Luminous intensity which is used for expressing the brightness of an LED, represents the light intensity of an optical source, as perceived by the human eye. The luminous intensity is measured in units of candela (cd), which is a base unit of the SI. This luminous intensity is given as Equation (2.2).

$$I = \frac{d\Phi_{lum}}{d\Omega} \tag{2.2}$$

Where  $\Omega$  is the spatial angle, and  $\Phi_{lum}$  is the luminous flux.

The illuminance is the luminous flux incident per unit area and it is measured in Lux  $(lm/m^2)$ . It is an SI unit used when characterizing illumination conditions. This is the main unit which can be used to measure the light intensity over an arbitrary area using the Lux meter. Being commercially available, Lux meter is used to characterize the light source. We have used Lux meter to verify the linear change of light over different dimming scenarios explained in more detail in Chapter 4.

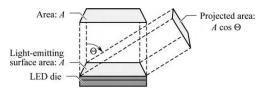

The luminance of a surface source is the ratio of the luminous intensity emitted in a certain direction (measured in cd) divided by the projected surface area in

Figure 2.2: Area of LED, A, and projected area, A  $\cos \Theta$  used for the definition of the luminance of an LED

| Photometric unit   | Dimension             | Radiometric unit             | Dimension   |

|--------------------|-----------------------|------------------------------|-------------|

| Luminous flux      | lm                    | Radiant flux (optical power) | W           |

| Luminous intensity | lm/sr = cd            | Radiant intensity            | W/sr        |

| Illuminance        | $lm/m^2 = lux$        | Irradiance (power density)   | $W/m^2$     |

| Luminance          | $lm/(srm^2) = cd/m^2$ | Radiance                     | $W/(srm^2)$ |

Table 2.1: Photometric and corresponding radiometric units

that direction (measured in  $m^2$ ). The luminance is measured in units of  $cd/m^2$ . In most cases, the direction of interest is normal to the chip surface. In this case, the luminance is the luminous intensity emitted along the chip-normal direction divided by the chip area. The projected surface area mentioned above follows a cosine law, *i.e.* the projected area is given by  $A_{projected} = A_{surface} \times \cos \Theta$ , where  $\Theta$  is the angle between the direction considered and the surface normal. The light-emitting surface area and the projected area are shown in Figure 2.2. The luminous intensity of LEDs with lambertian emission pattern also depends on the angle according to a cosine law. Accordingly, the luminance of lambertian LEDs is a constant, independent of angle. Photometric units are summarized in Table 2.1.

Brightness is an attribute of visual perception and is frequently used as synonym for luminance. To quantify the brightness of a source, it is useful to differentiate between point and surface area sources. For point sources, brightness can be approximated by the luminous intensity (measured in cd). For surface sources, brightness can be approximated by the luminance (measured in  $cd/m^2$ ).

Figure 2.3: Relation of maximum possible luminous efficacy and chromaticity

#### 2.3.1.2 Luminous Efficacy and Luminous Efficiency

This section describes the luminous efficacy as well as luminous efficiency which are the main two photometric units known to public showing the efficiency of the LED lamps.

The luminous efficacy of optical radiation (also called the luminosity function), measured in units of lumens per watt of optical power, is the conversion efficiency from optical power to luminous flux. The luminous efficacy is defined as

$$\frac{\Phi_{lum}}{P} = \frac{683\frac{lm}{W}\int_{\lambda} V(\lambda)P(\lambda)d\lambda}{\int_{\lambda} P(\lambda)d\lambda}$$

(2.3)

For strictly monochromatic light sources, the luminous efficacy is equal to the eye sensitivity function  $V(\lambda)$  multiplied by 683 lm/W. However, for multicolor light sources and especially for white light sources, the luminous efficacy needs to be calculated by integration over all wavelengths.

The luminous efficiency is shown on the right-hand side of Figure 2.3. The luminous efficiency of a light source, also measured in units of lm/W, is the luminous flux of the light source divided by the electrical input power, *i.e.*  $\Phi_{lum}/(I \times V)$ , where the product  $(I \times V)$  is the electrical input power of the device. In the lighting community, luminous efficiency is often referred to as luminous efficacy of the source. The luminous efficiency is the product of the luminous efficacy and the electricalto-optical power conversion efficiency. Table 2.2 summarizes frequently used figures

| Figure of merit               | Explanation                                            | Unit     |

|-------------------------------|--------------------------------------------------------|----------|

| Luminous efficacy             | Luminous flux per optical unit power                   | lm/W     |

| Luminous efficiency           | Luminous flux per input electrical unit power          | lm/W     |

| Luminous intensity efficiency | Luminous flux per $sr$ per input electrical unit power | cd/W     |

| Luminance                     | Luminous flux per $sr$ per chip unit area              | $cd/m^2$ |

Table 2.2: Summary of photometric performance measures for LEDs

of merit for LEDs.

The optical power emitted by a light source is then given by

$$P_t = \int_{\lambda} P(\lambda) d\lambda \tag{2.4}$$

This power indicates the total energy radiated from an LED. This formula is used in characterizing the received power of light which is discussed later in section 2.3.3.

In analyzing the VLC system it is required to have a good understanding of the optical power, the channel behavior and the received optical power (either the direct detection or its reflected one). In the following a brief definition of these quantities are given.

#### 2.3.2 Illuminance of LED Lighting

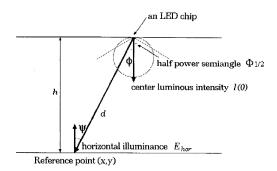

A horizontal illuminance, Ehor, at a point (x, y) is given by:

$$E_{hor} = I(0)\cos^{m}(\phi) / D_{d}^{2} \times \cos(\psi)$$

(2.5)

Where I(0) is the center luminous intensity of an LED,  $\phi$  is the angle of irradiance,  $\psi$  is the angle of incidence, and  $D_d$  is the distance between an LED and a detector's surface. For these formulas it is assumed that the LED chip has a Lambertian radiation pattern. Here m is the order of Lambertian emission, and is given by the semi-angle at half illuminace of an LED  $\Phi_{1/2}$  as  $m = \ln 2/\ln (\cos \Phi_{1/2})$ .

Figure 2.4: Horizontal illuminance of LED

#### 2.3.3 Received Power from LED Lights

In an optical channel, the DC gain is given as

$$H(0) = \begin{cases} \frac{(m+1)A}{2\pi D_d^2} \cos^m(\phi) T_s(\psi) g(\psi) \cos(\psi) & 0 \le \psi \le \Psi_c, \\ 0 & \psi > \Psi_c, \end{cases}$$

(2.6)

where A is the physical area of the detector,  $D_d$  is the distance between a transmitter and a receiver,  $\psi$  is the angle of incidence,  $\phi$  is the angle of irradiance,  $T_s(\psi)$  is the gain of an optical filter,  $g(\psi)$  is the gain of an optical concentrator, and  $\Psi_c$  denotes the width of the field of vision at a receiver.

The optical concentrator  $g(\psi)$  is given as:

$$g\left(\psi\right) = \begin{cases} \frac{n^2}{\sin^2 \Psi_c} & 0 \le \psi \le \Psi_c, \\ 0 & 0 \ge \Psi_c, \end{cases}$$

(2.7)

where n denotes the refractive index. The received optical power  $P_r$  is derived by the transmitted optical power  $P_t$  as follows:

$$P_r = H\left(0\right) \times P_t \tag{2.8}$$

where  $P_t$  is the average transmitted optical power and is given as  $P_t = \lim_{T \to \infty} \frac{1}{2T} \int_{-T}^{T} X(t) dt$ .

#### 2.3.4 Received Power of Reflected Light

Here the reflective effect of light by walls is also considered. The received power is given by the channel DC gain on directed path  $H_d(0)$  and reflected path  $H_{ref}(0)$ .

$$P_{r} = \sum \left\{ P_{t}H_{d}\left(0\right) + \int_{walls} P_{t}dH_{ref}\left(0\right) \right\}$$

$$(2.9)$$

The channel DC gain on the first reflection is as follows:

$$dH_{ref}\left(0\right) = \begin{cases} \frac{(m+1)A}{2\pi^2 D_1^2 D_2^2} \rho dA_{wall} \cos^m\left(\phi\right) \cos\left(\alpha\right) \cos\left(\beta\right) T_s\left(\psi\right) g\left(\psi\right) \cos\left(\psi\right), & 0 \le \psi \le \Psi_c \\ 0 & \psi > \Psi_c, \end{cases}$$

$$(2.10)$$

Where  $D_1$  is the distance between an LED chip and a reflective point,  $D_2$ is the distance between a reflective point and a receiver,  $\rho$  is the reflectance factor,  $dA_{wall}$  is a reflective area of small region,  $\phi$  is the angle of irradiance,  $\alpha$  is the angle of irradiance to a reflective point,  $\beta$  is the angle of irradiance to the receiver,  $\psi$  is the angle of incidence.

#### 2.3.5 Optical Wireless Channel

It is assumed that the noise in optical channel is an AWGN (additive white Gaussian noise). The dominant source of noise in optical channel is known to be shot noise. A typical transmitted signal contain a time varying shot noise process which has an average rate of  $10^4$  to  $10^5$  photons per bit. It is probable that in an optical channel model the intense light striking the detector leads to a steady shot noise which has a rate of order of  $10^7$  to  $10^8$  photons per bit and as a result the shot noise caused by signals can be neglected. With this assumption the ambient-induced shot noise can be modeled as a Gaussian process. Also when little or no ambient light is present, the dominant noise source is receiver noise, which is also signal independent and Gaussian. All things considered, the optical wireless channel model is expressed as:

$$Y(t) = \gamma X(t) \oplus h(t) + N(t)$$

(2.11)

where Y(t) represents the received signal current,  $\gamma$  is the detector responsivity, X(t) represents the transmitted optical pulse, h(t) is the impulse response, N(t) represents the AWGN, and the symbol  $\oplus$  denotes convolution. In VLC, the LEDs which have the function of communication have a wide irradiance angle because they also used for function of lighting equipment. As a result a non-directed LOS path is assumed.

It has been mentioned that VLC is a promising technology which takes advantage of LED devices. Study and analysis of LEDs is an essential part of VLC system design. In the following section of this introduction, after describing the operation of LED lamps and its different types the white LEDs, modulation characteristics as well as transient and frequency response of LEDs are explained in detail. This analysis offers vital clues in alleviating the low bandwidth limitation of white LEDs. These clues, indeed, open the doors to the invention of state of the art LED driver circuit design for high speed data transmission and dimming control.

### 2.4 White LED

LED is an optoelectronic device which generates light. It contains a P-N junction, through which an electric current is sent. In the heterojunction, the current generates electrons and holes, which release their energy portions as photons when they recombine. Two basic types of semiconductor optical sources exist: The LEDs and laser diodes (LD). Laser diodes are used for long distance, high data rate transmissions, while LED devices are used for shorter distance, lower data rate transmission. LED operation is based on spontaneous emission, while the laser operation is based on spontaneous emission, while the principle of operation is based on the interaction of light and matter with a semiconductor material.

Since, the incandescent lamp was invented by Edison in 1882, artificial lighting has passed through three phases incandescent lamp, neon light, and discharge lamp, and has been advancing towards the fourth phase of semiconductor lighting, especially white LEDs. In well under a decade, LEDs have expanded their role from

| Material         | Typical emission wavelengths |

|------------------|------------------------------|

| InGaN / GaN, ZnS | $450 \ 530 \ nm$             |

| GaP:N            | $565 \ nm$                   |

| AlInGaP          | $590\ \ 620\ nm$             |

| GaAsP, GaAsP:N   | 610 $650$ $nm$               |

| InGaP            | $660 \ 680 \ nm$             |

| AlGaAs, GaAs     | $680 \ 860 \ nm$             |

| InGaAsP          | $1000 \ 1700 \ nm$           |

Table 2.3: Semiconductor materials and emission wavelengths

little red spots to brilliant white light sources capable of illuminating a room or lighting the road ahead.

Practical white LEDs were made possible by work with GaN semiconductor materials in the 1990s by Dr. Shuji Nakamura at Nichia Corporation in Japan. He first achieved blue and green LEDs. Nakamura's next step was placing a novel phosphor over his blue chip to get a white light, and finally he worked on the blue laser.

The center wavelength and thus the emission color of an LED are largely determined by the bandgap energy of the semiconductor material used. Essentially the whole visible wavelength region can be covered with LEDs, although the achievable power output and efficiency is not equally high for all wavelengths.

Table 2.3 shows the semiconductor materials and emission wavelengths. White light can be generated either by mixing the outputs of e.g. red, green and blue LEDs, or by using a single blue LED and some phosphor, which converts part of the blue light into a light with longer wavelengths.

#### 2.4.1 Types of White LEDs

Two types of white-light LEDs used in lighting:

- Devices that use separate red green blue (RGB) emitters.

- Those that use a blue emitter in combination with a phosphor that emits yellow light.

The color of white LEDs comes from the narrow-band blue naturally emitted by GaN LEDs, plus a broad spectrum yellow generated by a phosphor coating on the die which absorbs a proportion of the blue and converts it to yellow. GaN die are InGaN hetero-structures, which can produce operational wavelengths from green to ultra-violet by varying the relative amounts of indium and gallium during production. Although this blue die plus yellow phosphor approach yields light which appears white, it has little green and almost no red content leading to inferior color rendering compared with incandescent bulbs and even tri-phosphor florescent tubes. Warm white LEDs, which include a red-producing phosphor, are an attempt to improve this situation as well as make LEDs illumination more acceptable in living spaces.

### 2.5 LED Modulation Characteristics