# Gigascale Silicon Photonic Transmitters Integrating HBTbased Carrier-injection Electroabsorption Modulator Structures

A dissertation submitted by

### Enjin Fu

In partial fulfillment of the requirements for the degree of

Doctor of Philosophy

in

**Electrical Engineering**

### **TUFTS UNVERSITY**

August, 2015

# Advisor: Prof. Valencia Joyner Koomson

For my family

#### Abstract

Demand for more bandwidth is rapidly increasing, which is driven by data intensive applications such as high-definition (HD) video streaming, cloud storage, and terascale computing applications. Next-generation high-performance computing systems require power efficient chip-to-chip and intra-chip interconnect yielding densities on the order of 1Tbps/cm<sup>2</sup>. The performance requirements of such system are the driving force behind the development of silicon integrated optical interconnect, providing a cost-effective solution for fully integrated optical interconnect, optical interconnects have several advantages, including frequency independent insertion loss resulting in ultra wide bandwidth and link latency reduction.

For high-speed optical transmitter modules, the optical modulator is a key component of the optical I/O channel. This thesis presents a silicon integrated optical transmitter module design based on a novel silicon HBT-based carrier injection electroabsorption modulator (EAM), which has the merits of wide optical bandwidth, high speed, low power, low drive voltage, small footprint, and high modulation efficiency. The structure, mechanism, and fabrication of the modulator structure will be discussed which is followed by the electrical modeling of the post-processed modulator device. The design and realization of a 10Gbps monolithic optical transmitter module integrating the driver circuit architecture and the HBT-based EAM device in a 130nm BiCMOS process is discussed. For high power efficiency, a 6Gbps ultra-low power driver IC implemented in a 130nm BiCMOS process is presented. The driver IC incorporates an integrated 2<sup>7</sup>-1 pseudo-random bit sequence (PRBS) generator for reliable high-speed testing, and a driver circuit featuring digitally-tuned pre-

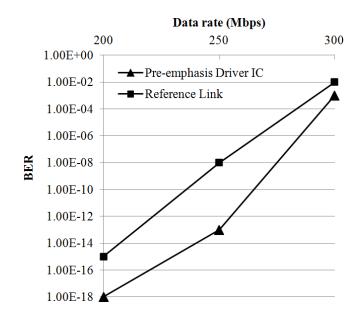

emphasis signal strength. With outstanding drive capability, the driver module can be applied to a wide range of carrier injection modulators and light-emitting diodes (LED) with drive voltage requirements below 1.5V. Measurement results show an optical link based on a 70MHz red LED work well at 300Mbps by using the pre-emphasis driver module. A traveling wave electrode (TWE) modulator structure is presented, including a novel design methodology to address process limitations imposed by a commercial silicon fabrication technology. Results from 3D full wave EM simulation demonstrate the application of the design methodology to achieve specifications, including phase velocity matching, insertion loss, and impedance matching. Results show the HBT-based TWE-EAM system has the bandwidth higher than 60GHz.

#### Acknowledgement

First and foremost, I am deeply indebted to my advisor Prof. Valencia Joyner Koomson for her continuous encouragement, mentorship and support. I cannot overstate how influential Prof. Koomson has been for my personal and professional developments. Her inspiration was essential to the completion of this dissertation.

I would like to thank my thesis committee members: Prof. Mohammed N. Afsar, Prof. Mark Cronin-Golomb from Tufts biomedical department, and Prof. Ronald W. Knepper from ECE department at Boston University for their time and dedication. Thanks for their insightful suggestions on this work.

I would like to thank Prof. Z. Rena Huang and my colleagues Pengfei Wu and Shengling Deng at RPI for their continuous help and inspiration of the collaborative optical modulator project. I would like to thank Prof. Afsar and my colleagues Liu Chao, Tinghao Liang, Hassan Oukacha, Jun Jadormio, Kate Auerbach, Wei Wang at Tufts for their great cooperation of the CMOS integrated microwave circulator project. It's so exciting to work on both cutting-edge projects with them.

I would like to thank Prof. Sameer Sonkusale for teaching me analog and mixed signal circuits design and letting me have access to the test instruments in Nanolab. Thanks Prof. Knepper at Boston University for teaching me radio frequency circuits design. He was always willing to answer all my questions. Meanwhile, I would like to thank Prof. Joseph Noonan, his "Communication systems" course is the most funny and also informative one I ever taken. Also, I would like to thank Prof. Tom Vandevalde for his insightful suggestions to this research project.

Special thanks to Cheng Li at Hewlett-Packard Laboratory for his useful discussion about this research project. His papers inspired me a lot of good ideas. I would like to thank Saroj Rout and Pramod Singh for their precious help and discussion about the circuits design. They are always nice and helpful.

Also, I would like to thank my Qorvo colleagues: Mike Coolen for his help about RF PCB design, and Ginny Bouthillette for her help about chip-onboard wirebonding.

I would like to thank my lab fellows Ali Mirvakili, Chirag Sthalekar, Ruida Yun. It's very lucky to work with them in the same lab, I would never forget about it. I would like to thank all the other lab colleagues: Pooria Mostafalu, Ninrat Datiri, Chenguang Xi, Shideh Kabiri, Saber Bahranifard, Zhengxin Zhao, Kyoungchul Park, Sam MacNaughton, Guoqing Fu, Meera Punjiya, Robbie D'Angelo, Krener Konomi, Yun Miao, Yu Chen, Chiamaka Chima, Nana Kwakwa, Stephen Akaeze, Barbara Gyasi, Jian Guo, Wangren Xu, and my friends at ECE department: Hao Zhang, Chen Gao, Jincheng Pang, Ruiling Gao, Yuping Dong, Anjali Sharma, Yuanwei Wu. Forgive me if I miss any names here. It's really nice to meet them in my life.

I would like to thank all the administrative staffs at Halligan: Miriam Santi, Jennifer St Pierre, Ilse Allen, Renee Simonetti, Merrianne Terranova for their great assistance. I want to state my appreciation and gratitude to George Preble, Eric Patton, Patrick Hynes, Mike Bauer, Jon Fredrick for their support in handling any technical matters. The international center advisors are amongst the best and they were always happy to provide help. I would like to thank Jane Etish-Andrews, Lois Hutchings, Naoko Kotoge, Carol Murphy and Whitney Sullivan. They are one of the important reasons why I love Tufts so much.

The most important, I would like to thank my family for their great support. Without their encouragement and understanding, I could not finish this dissertation.

# Contents

| Dedication                                                       | ii  |

|------------------------------------------------------------------|-----|

| Abstract                                                         | iii |

| Acknowledgement                                                  | v   |

| List of Figures                                                  | X   |

| List of Tables                                                   | XV  |

| Chapter 1 Introduction                                           | 1   |

| 1.1 Data communication                                           | 1   |

| 1.2 Optical interconnect VS electrical interconnect              | 2   |

| 1.3 Silicon photonics                                            | 8   |

| 1.4 Silicon photonics on SiGe BiCMOS substrate                   | 12  |

| 1.5 Thesis organization                                          | 15  |

| Chapter 2 SiGe HBT-based Carrier Injection Electroabsorption     |     |

| Modulator                                                        | 16  |

| 2.1 Optical communication systems                                | 16  |

| 2.1.1 Application                                                | 16  |

| 2.1.2 Key specifications                                         | 18  |

| 2.2 Optical modulator                                            | 25  |

| 2.2.1 Free carrier plasma effect                                 | 26  |

| 2.2.2 Silicon modulator varieties                                | 27  |

| 2.2.3 Carrier injection VS Carrier depletion                     | 29  |

| 2.2.4 Ideal modulator                                            | 31  |

| 2.3 SiGe HBT-based Carrier Injection Electroabsorption Modulator | 22  |

| 2.3.   | 1 Device structure                                          | . 32 |

|--------|-------------------------------------------------------------|------|

| 2.3.   | 2 Optical property                                          | . 34 |

| 2.3.   | 3 Speed                                                     | . 35 |

| 2.3.   | 4 Extinction ratio                                          | . 36 |

| 2.3.   | 5 Fabrication                                               | . 38 |

| 2.3.   | 6 Electrical Model                                          | . 38 |

| 2.4    | Summary                                                     | . 40 |

| Chapte | er 3 A 10Gbps monolithic optical transmitter module design  | . 42 |

| 3.1    | Modulator physical design                                   | . 42 |

| 3.2    | Modulator electrical interface                              | . 44 |

| 3.3    | Modulator driver                                            | . 47 |

| 3.4    | Layout and fabrication                                      | . 53 |

| 3.5    | Chip post-processing                                        | . 56 |

| 3.6    | Optical measurement                                         | . 57 |

| 3.7    | Electrical measurement                                      | . 58 |

| 3.8    | Summary                                                     | . 62 |

| Chapte | er 4 A ultra-low power optical driver design                | . 64 |

| 4.1    | Block diagram                                               | . 65 |

| 4.2    | Pre-emphasis driver                                         | . 66 |

| 4.3    | Pre-driver                                                  | . 69 |

| 4.4    | 2 <sup>7</sup> -1 pseudo-random bit stream (PRBS) generator | . 70 |

| 4.5    | Chip fabrication and floorplan                              | . 78 |

| 4.6    | Measurement results                                         | . 79 |

| 4.6.   | 1 RF PCB testbench                                          | . 79 |

| 4.6.   | 2 Probe station testbench                                   | . 85 |

| 4.7     | Results with modulator load |                                                           |     |

|---------|-----------------------------|-----------------------------------------------------------|-----|

| 4.8     | Performance comparison      |                                                           |     |

| 4.9     | Sur                         | nmary                                                     | 91  |

| Chapte  | er 5                        | 300Mbps LED Link with Bandwidth Enhancement by usin       | g   |

| Pre-em  | npha                        | sis driver                                                | 92  |

| 5.1     | LE                          | D data communication link                                 | 93  |

| 5.2     | LE                          | D module                                                  | 94  |

| 5.3     | Tes                         | tbench and measurement                                    | 97  |

| 5.4     | Sur                         | nmary                                                     | 101 |

| Chapte  | er 6                        | A traveling wave electrode electroabsorption modulator (T | WE- |

| EAM)    | desi                        | gn in a commercial process                                | 102 |

| 6.1     | ΤW                          | /E-EAM distributed model                                  | 103 |

| 6.2     | Des                         | sign target                                               | 111 |

| 6.3     | HB                          | T-based TWE-EAM design methodology                        | 112 |

| 6.3.    | 1                           | $\mu_{p,e}$ design                                        | 113 |

| 6.3.    | 2                           | Impedance matching design                                 | 117 |

| 6.3.    | 3                           | <i>C</i> <sub>decpl</sub> design                          | 118 |

| 6.4     | Res                         | sults                                                     | 119 |

| 6.4.    | 1                           | MIM Capacitor <i>C</i> <sub>decpl</sub>                   | 119 |

| 6.4.    | 2                           | TWE-HBT-EAM simulation                                    | 120 |

| 6.5     | Sur                         | nmary                                                     | 124 |

| Chapte  | er 7                        | Conclusion and Future Work                                | 126 |

| 7.1     | Co                          | nclusion                                                  | 126 |

| 7.2     | Fut                         | ure work                                                  | 128 |

| Bibliog | grap                        | hy                                                        | 130 |

## List of Figures

| Figure 1.1: Global IP traffic forecast [1]1                                      |

|----------------------------------------------------------------------------------|

| Figure 1.2: Electrical interconnect system                                       |

| Figure 1.3: Optical interconnect system                                          |

| Figure 1.4: Loss comparison of board-to-board interconnect                       |

| Figure 1.5: Supercomputer "Sequoia" invented by IBM [9] 4                        |

| Figure 1.6: Loss comparison of on-chip interconnect                              |

| Figure 1.7: Comparison of the energy/bit of the low-latency interconnect options |

| in a 22 nm logic node [15]                                                       |

| Figure 1.8: Hybrid integration of a OE system                                    |

| Figure 1.9: Monolithic integration of a OE system (silicon photonics)            |

| Figure 1.10: Silicon photonics [16][17][18] 10                                   |

| Figure 1.11: NMOS FET in SOI process11                                           |

| Figure 1.12: Optical waveguide/modulator on a SOI wafer11                        |

| Figure 1.13: SiGe HBT device cross-section view                                  |

| Figure 1.14: SiGe HBT and silicon NMOS on a same substrate14                     |

| Figure 1.15: Adapted photonics friendly SiGe BiCMOS process 15                   |

| Figure 2.1: Applications of optical communication [42] 17                        |

| Figure 2.2: Optical communication system                                         |

| Figure 2.3: Format of NRZ and RZ signal                                          |

| Figure 2.4: Spectrum of NRZ signal                                               |

| Figure 2.5: Spectrum of RZ signal                                                |

| Figure 2.6: 2 <sup>3</sup> -1 PRBS generator                                     |

| Figure 2.7: 2 <sup>3</sup> -1 PRBS signal                                        |

| Figure 2.8: spectrum of PRBS signal                                              |

| Figure 2.9: how an eye diagram formed 22                                         |

| Figure 2.10: (a) Jitter and (b) noise                                            |

| Figure 2.11: Jitter components                                                    |

|-----------------------------------------------------------------------------------|

| Figure 2.12: Logic error                                                          |

| Figure 2.13: WDM transceiver system                                               |

| Figure 2.14: Internal modulation                                                  |

| Figure 2.15: External modulation                                                  |

| Figure 2.16: Mach-Zehnder Interferometer                                          |

| Figure 2.17: EA modulator                                                         |

| Figure 2.18: Micro-ring modulator[49]                                             |

| Figure 2.19: Modulator types (a) injection (b) depletion [19]                     |

| Figure 2.20: Desired modulator features                                           |

| Figure 2.21: HBT-device in a SiGe BiCMOS process                                  |

| Figure 2.22: Idea of a HBT-based optical modulator                                |

| Figure 2.23: Designed HBT-based optical modulator with dimensions [55] 34         |

| Figure 2.24: (a) TM mode OFF state, (b) TM mode ON state [55]35                   |

| Figure 2.25: Transient response of HBT modulator [55]                             |

| Figure 2.26: Post-processing steps                                                |

| Figure 2.27: Current flow in subcollector                                         |

| Figure 2.28: Parasitic capacitance from sub-collector to the substrate. Left:     |

| original HBT device with large parasitic; right: modified HBT device with small   |

| parasitic                                                                         |

| Figure 2.29: Electrical model and driving interface of the carrier injection HBT- |

| based EAM                                                                         |

| Figure 3.1: Take off deep trench layer along the light path                       |

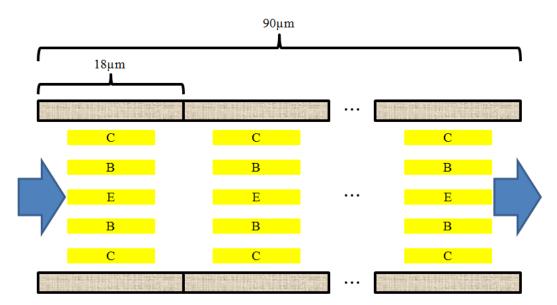

| Figure 3.2: Parallel connect multiple HBTs                                        |

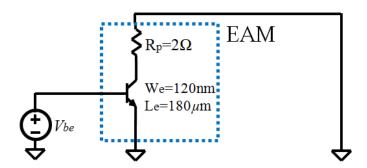

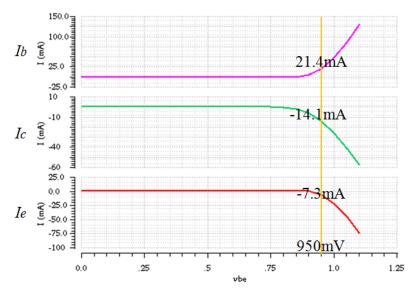

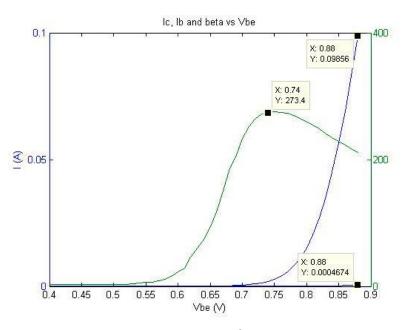

| Figure 3.3: DC characterization with sweep of V <sub>be</sub>                     |

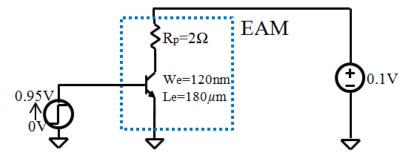

| Figure 3.4: DC $I_b$ , $I_c$ , and $I_e$ with sweep of $V_{be}$                   |

| Figure 3.5: Modulator driving interface (ideal)                                   |

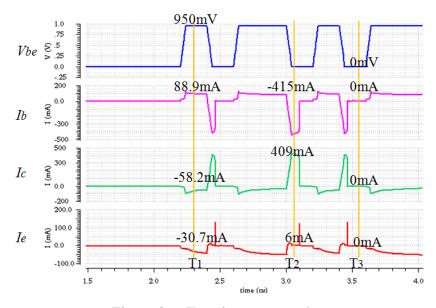

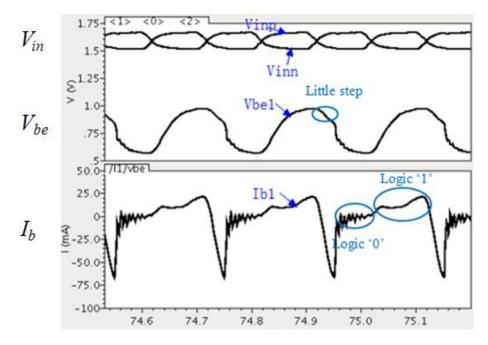

| Figure 3.6: Transient $I_b$ , $I_c$ , and $I_e$                                   |

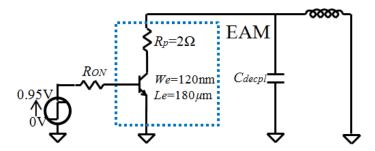

| Figure 3.7: Modulator driving interface (realistic)                               |

| Figure 3.8: Transient simulation with parasitic                                   |

| Figure 3.9: Driver block diagram                                                  |

| Figure 3.10: Amplifier circuit                                                                              |

|-------------------------------------------------------------------------------------------------------------|

| Figure 3.11: <i>V</i> <sub>bias1</sub> controls the swing of <i>V</i> <sub>out</sub>                        |

| Figure 3.12: $V_{bias2}$ controls the DC bias of $V_{out}$                                                  |

| Figure 3.13: Emitter follower buffer (a) precise and (b) coarse current source 51                           |

| Figure 3.14: post-layout transient simulation results of driver                                             |

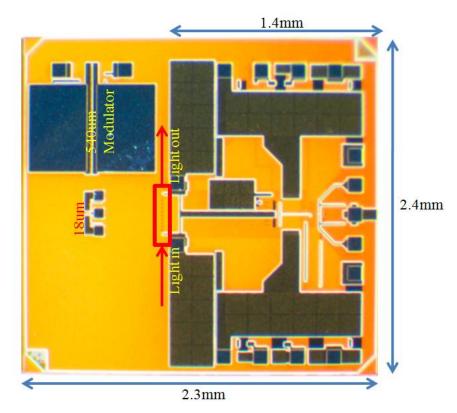

| Figure 3.15: The microphotograph of chip layout                                                             |

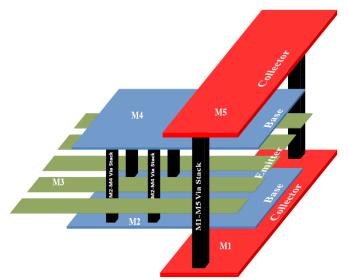

| Figure 3.16: Cross-sectional view of routing scheme for the modulator device 55                             |

| Figure 3.17: Scheme of connecting two bases and collectors together                                         |

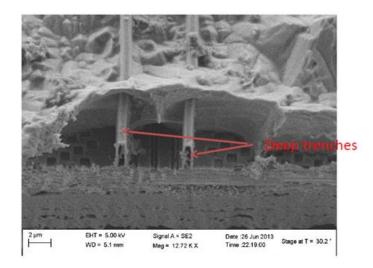

| Figure 3.18: SEM picture after backside polishing and fine etch                                             |

| Figure 3.19: SEM picture after front-end laser cutting                                                      |

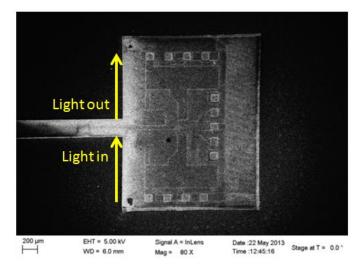

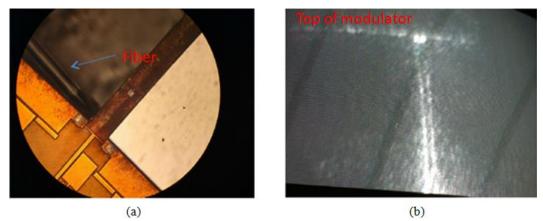

| Figure 3.20: Light coupling through subcollector                                                            |

| Figure 3.21: Light coupling through the collector and base area                                             |

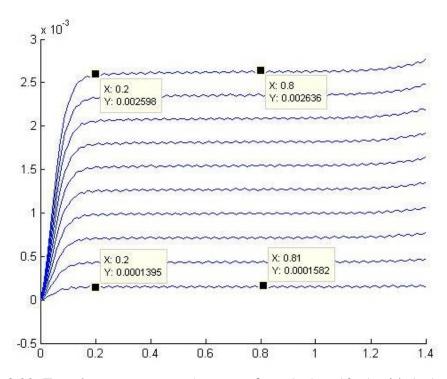

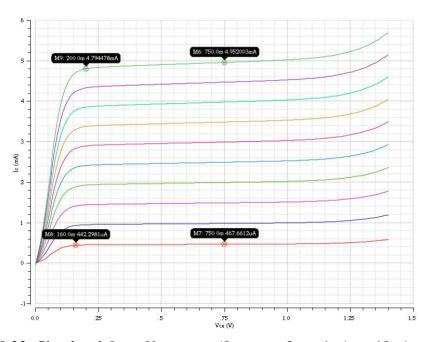

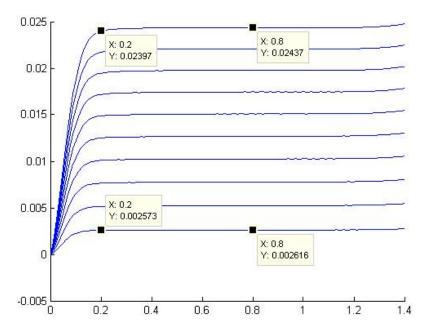

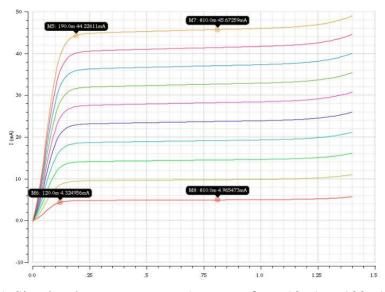

| Figure 3.22: Tested $I_c$ vs $V_{ce}$ curves ( $I_b$ sweep from $1\mu$ A to $10\mu$ A with $1\mu$ A step)59 |

| Figure 3.23: Simulated $I_c$ vs $V_{ce}$ curves ( $I_b$ sweep from $1\mu$ A to $10\mu$ A with $1\mu$ A      |

| step)                                                                                                       |

| Figure 3.24: Tested $I_c$ vs $V_{ce}$ curves ( $I_b$ sweep from $10\mu$ A to $100\mu$ A with $10\mu$ A      |

| step)                                                                                                       |

| Figure 3.25: Simulated $I_c$ vs $V_{ce}$ curves ( $I_b$ sweep from $10\mu$ A to $100\mu$ A with $10\mu$ A   |

| step)                                                                                                       |

| Figure 3.26: tested $I_c$ , $I_b$ and $\beta$ versus $V_{be}$ curves                                        |

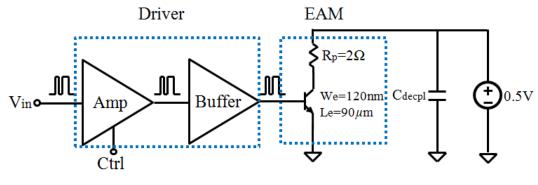

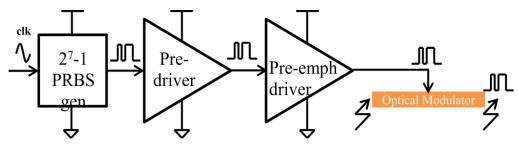

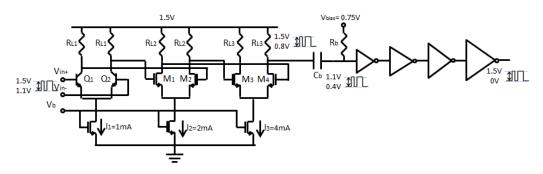

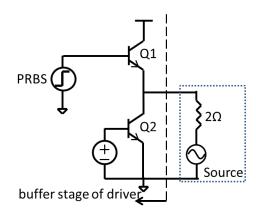

| Figure 4.1: HBT-based EAM transmitter circuit                                                               |

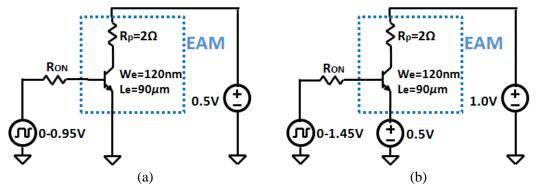

| Figure 4.2: Electrical model and driving interface of HBT EAM (a) regular, and                              |

| (b) all terminal biases raised by 0.5V                                                                      |

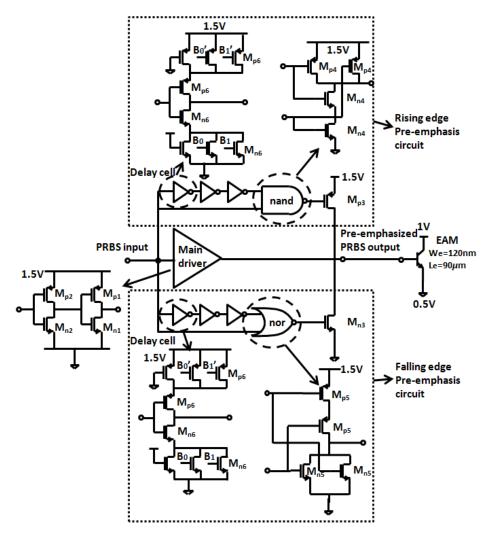

| Figure 4.3: Pre-emphasis driver circuit schematic                                                           |

| Figure 4.4: Pre-driver circuit                                                                              |

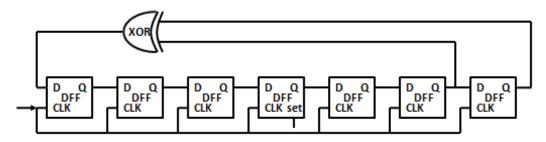

| Figure 4.5: 2 <sup>7</sup> -1 PRBS generator circuit                                                        |

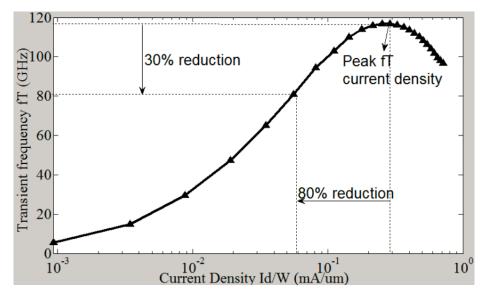

| Figure 4.6: Trade-off between current density and $f_T$ of a MOSFET (W=3.2 $\mu$ m,                         |

| L=120nm) in the 130nm BiCMOS process                                                                        |

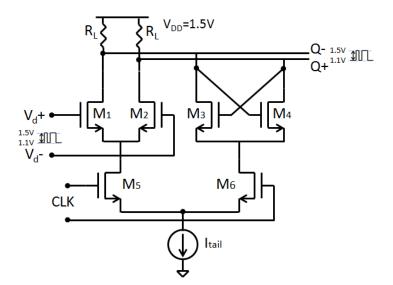

| Figure 4.7: CML low-power D-latch                                                                           |

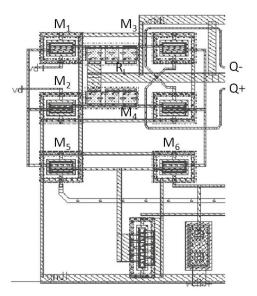

| Figure 4.8: floorplan of CML latch                                                                          |

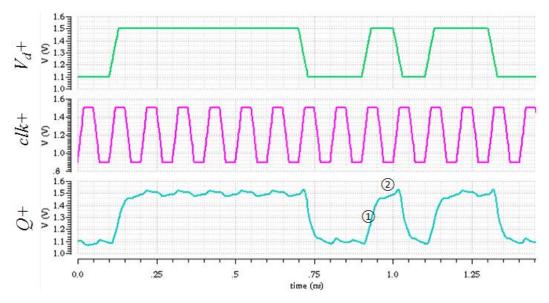

| Figure 4.9: post layout transient simulation results of CML latch74                                         |

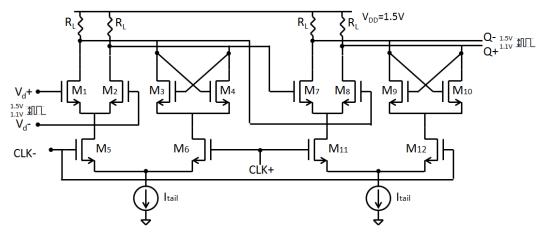

| Figure 4.10: Master-slave DFF                                               | . 75 |

|-----------------------------------------------------------------------------|------|

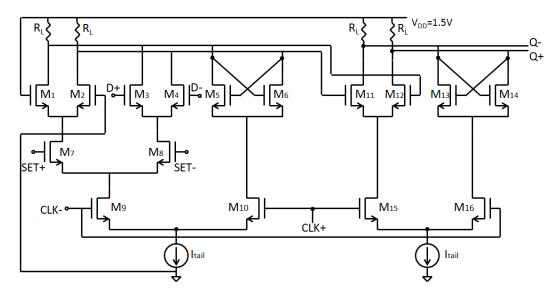

| Figure 4.11: DFF with SET function circuit                                  | . 75 |

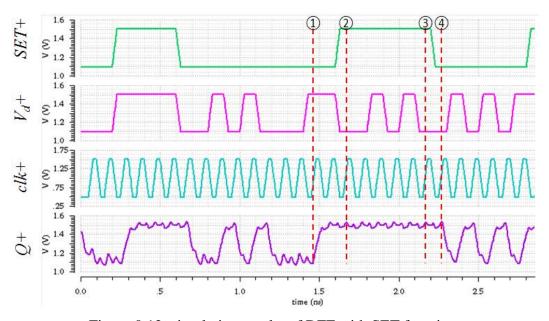

| Figure 4.12: simulation results of DFF with SET function                    | . 76 |

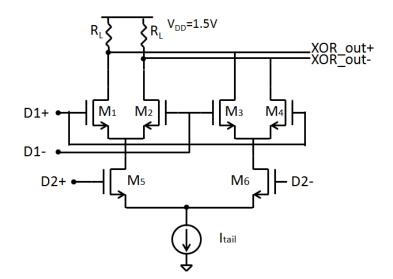

| Figure 4.13: XOR gate circuit                                               | . 77 |

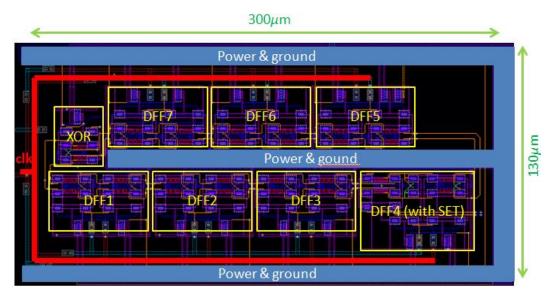

| Figure 4.14: the layout of PRBS generator                                   | . 78 |

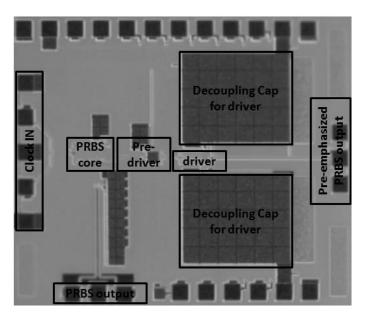

| Figure 4.15: Chip microphotograph                                           | . 79 |

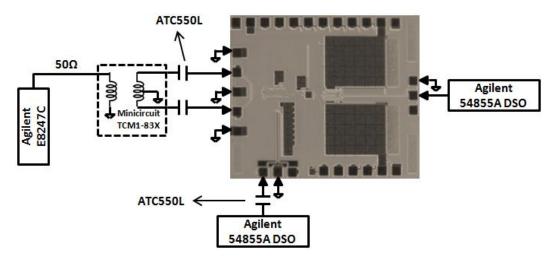

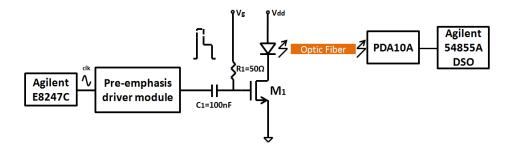

| Figure 4.16: PCB testbench block diagram                                    | . 80 |

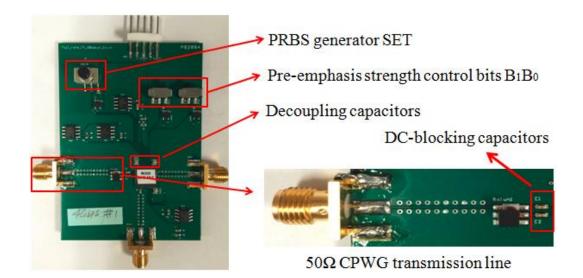

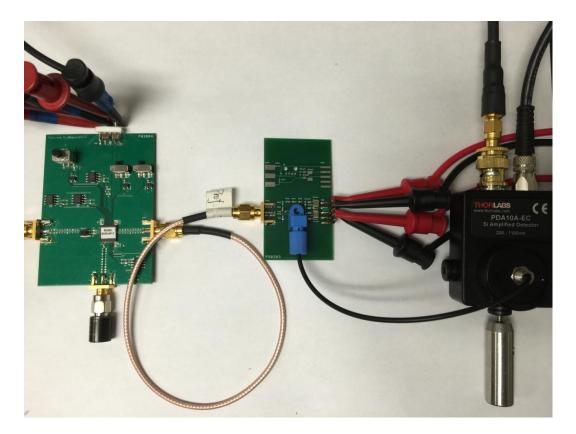

| Figure 4.17: PCB testbench picture                                          | . 81 |

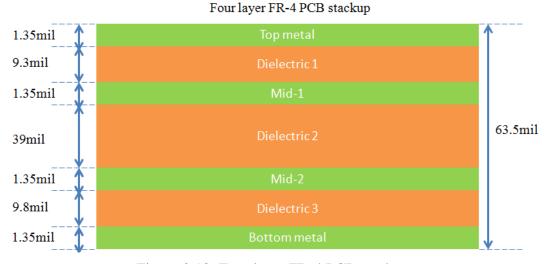

| Figure 4.18: Four layer FR-4 PCB stackup                                    | . 81 |

| Figure 4.19: CPWG design using ADS Linecalc                                 | . 82 |

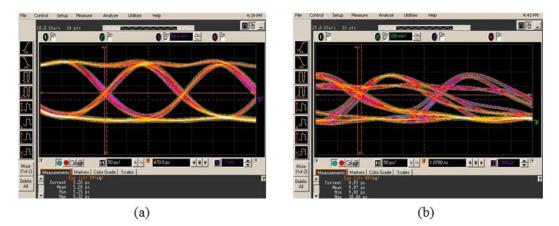

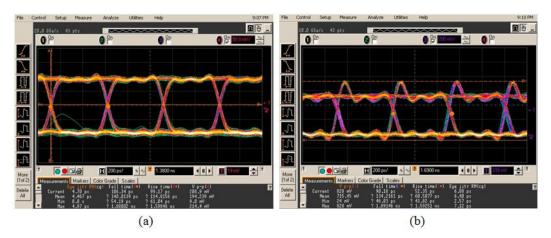

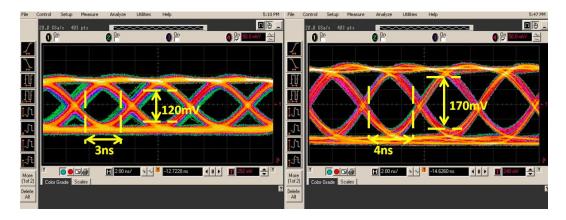

| Figure 4.20: 5.5Gbps Eye diagram of output signals                          | . 82 |

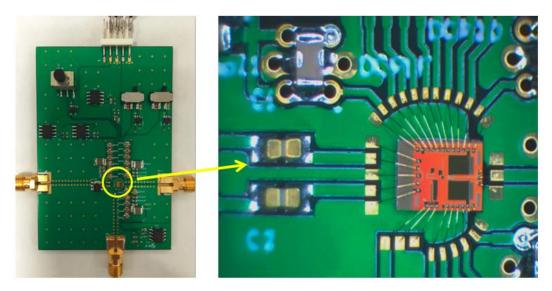

| Figure 4.21: chip-on-board assembly                                         | . 83 |

| Figure 4.22: 2Gbps Eye diagram of output signals                            | . 84 |

| Figure 4.23: Control the pre-emphasis strength                              | . 84 |

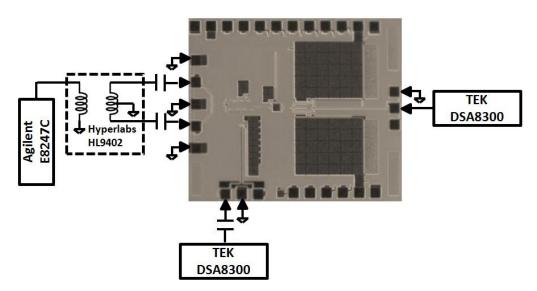

| Figure 4.24: Probe station testbench block diagram                          | . 85 |

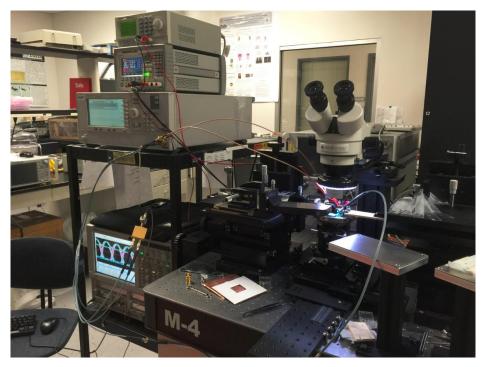

| Figure 4.25: Probe station testbench picture                                | . 86 |

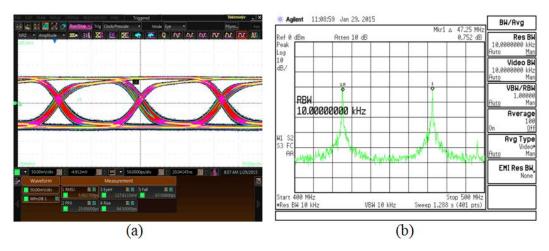

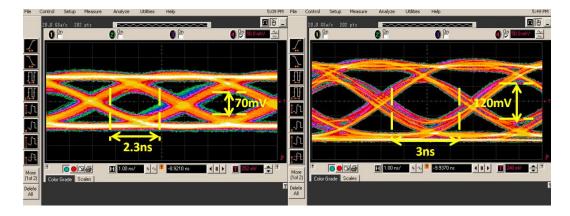

| Figure 4.26: 6Gbps PRBS signal (a) eye diagram and (b) spectrum             | . 86 |

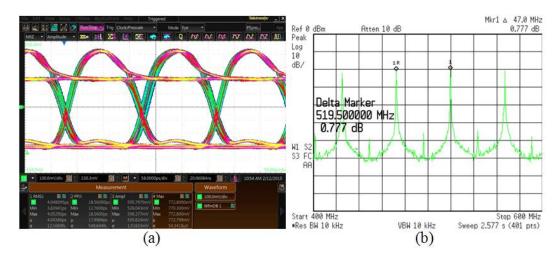

| Figure 4.27: 6Gbps pre-emphasis (strong) PRBS signal (a) eye diagram and    | (b)  |

| spectrum                                                                    | . 87 |

| Figure 4.28: 6Gbps pre-emphasis (strong and weak) PRBS signal               | . 88 |

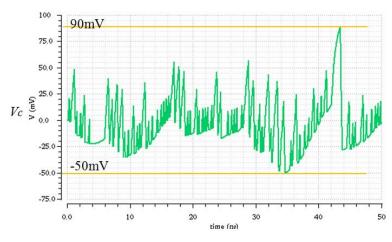

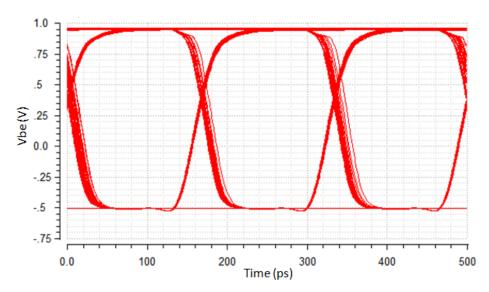

| Figure 4.29: 6Gbps driver output signal at HBT modulator load               | . 88 |

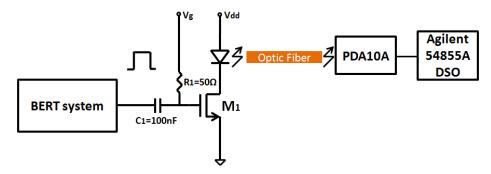

| Figure 5.1: Data transmission link with regular transmitter                 | . 94 |

| Figure 5.2: Data transmission link with pre-emphasis transmitter            | . 94 |

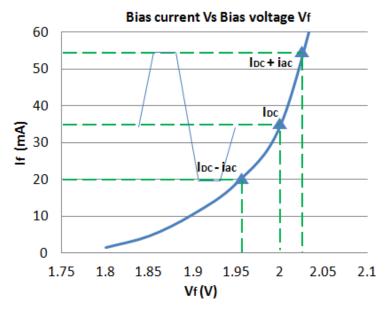

| Figure 5.3: I-V curve of LED                                                | . 95 |

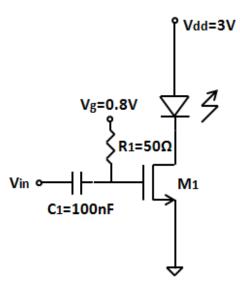

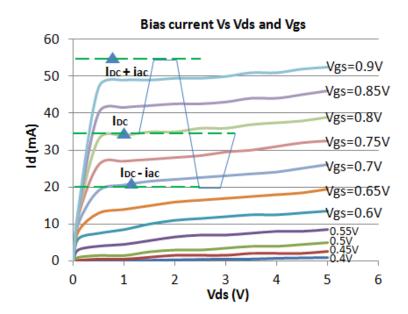

| Figure 5.4: LED and switch schematic                                        | . 95 |

| Figure 5.5: I-V curve of MOSEFT switch                                      | . 96 |

| Figure 5.6: PCB testbench (with input from pre-emphasis driver)             | . 97 |

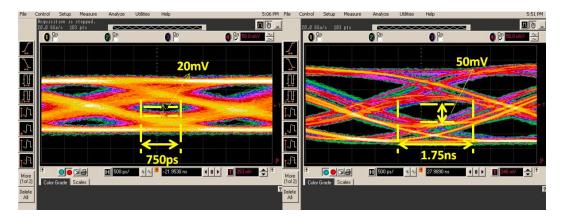

| Figure 5.7: 200Mbps eye diagram (a) with input from BERT system (b) with in | put  |

| from pre-emphasis driver                                                    | . 98 |

| Figure 5.8: 250Mbps eye diagram (a) with input from BERT system (b) with in | put  |

| from pre-emphasis driver                                                    | . 99 |

| Figure 5.9: 300Mbps eye diagram (a) with input from BERT system (b) with input                |

|-----------------------------------------------------------------------------------------------|

| from pre-emphasis driver                                                                      |

| Figure 6.1: Cross-section view of HBT-based modulator 104                                     |

| Figure 6.2: Side-view of modulator at A-A' 104                                                |

| Figure 6.3:Lumped electrical model of HBT-based modulator. (a)Simplified                      |

| model (b) Realistic model with $L_{wire}$ and on-chip $C_{decpl}$                             |

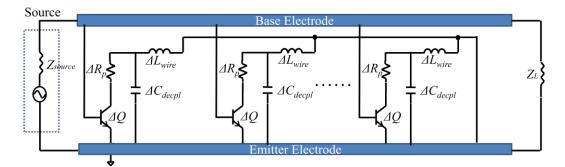

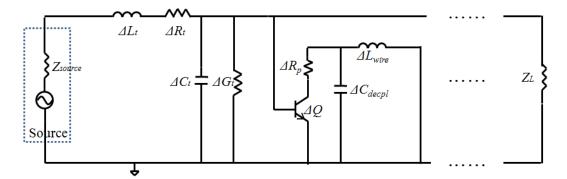

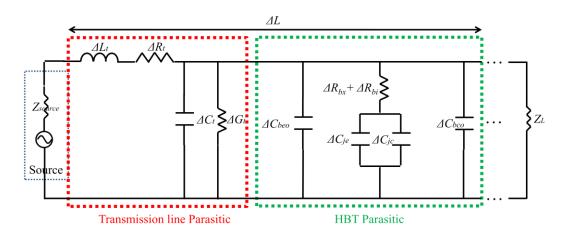

| Figure 6.4: Distributed model of HBT-based modulator with source and load 100                 |

| Figure 6.5: distributed model of TWE-EAM device 100                                           |

| Figure 6.6: HBT VBIC model 10                                                                 |

| Figure 6.7: simplified HBT VBIC equivalent circuit110                                         |

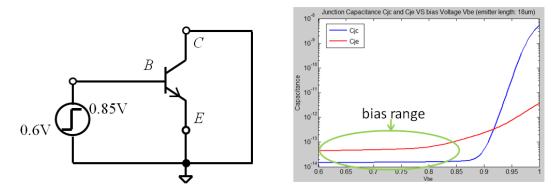

| Figure 6.8: $C_{je}$ and $C_{jc}$ VS $V_{be}$ of an 18 $\mu$ m HBT in the 130nm BiCMOS proces |

|                                                                                               |

| Figure 6.9: Complete small signal model of HBT-TWE11                                          |

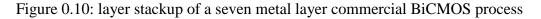

| Figure 6.10: layer stackup of a seven metal layer commercial BiCMOS proces                    |

|                                                                                               |

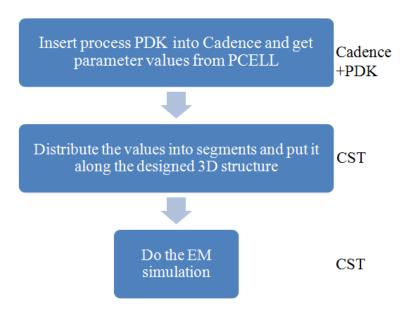

| Figure 6.11: Cadence and CST Microwave Studio Co-simulation112                                |

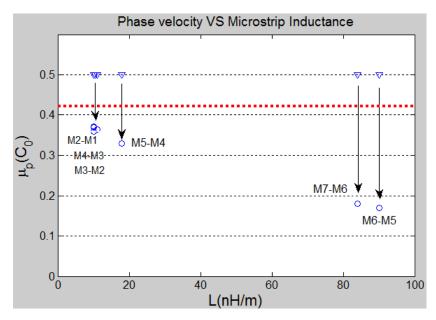

| Figure 6.12: Phase velocity Vs microstrip inductance (triangular marker: without              |

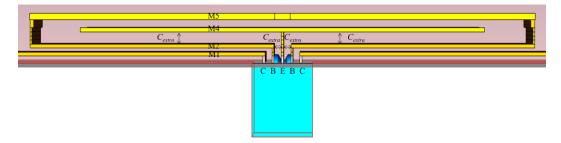

| EAM model, circular marker: with EAM model)110                                                |

| Figure 6.13: Cross-section view of TWE for the HBT-based EAM110                               |

| Figure 6.14: simulation setup of S <sub>22</sub> of driver118                                 |

| Figure 6.15: Simulation results of S <sub>22</sub> of driver118                               |

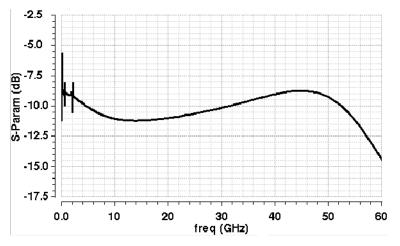

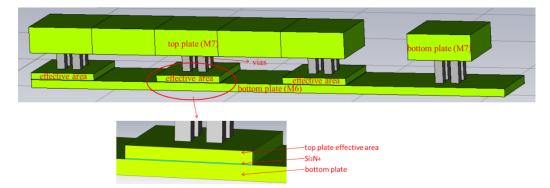

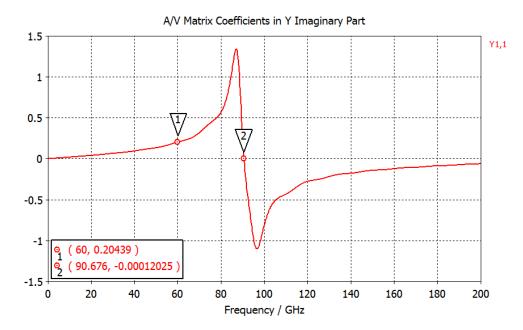

| Figure 6.16: 300fF MIM capacitor works up to 90GHz119                                         |

| Figure 6.17: Imaginary part of admittance of the 300fF MIM capacitor 120                      |

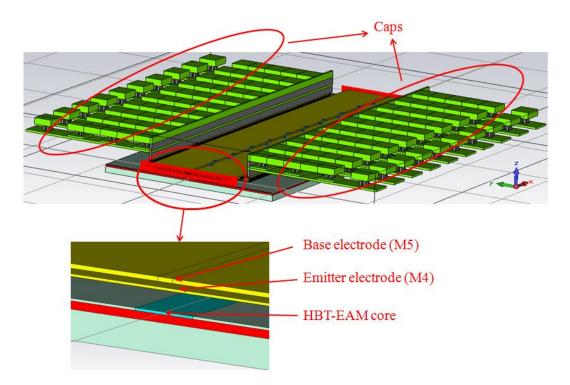

| Figure 6.18: The 3D view of TWE-HBT-EAM (left: the whole structure, right                     |

| zoom-in of the HBT-EAM region)12                                                              |

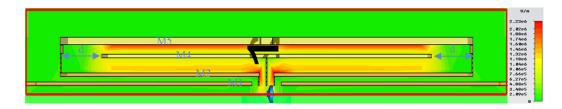

| Figure 6.19: E-field of the TWE-HBT-EAM 12                                                    |

| Figure 6.20: Dispersion simulation of TWE waveguide (green: without HBT                       |

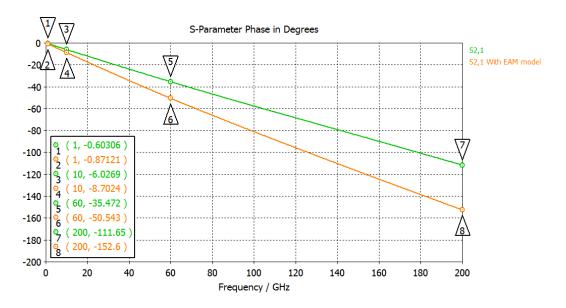

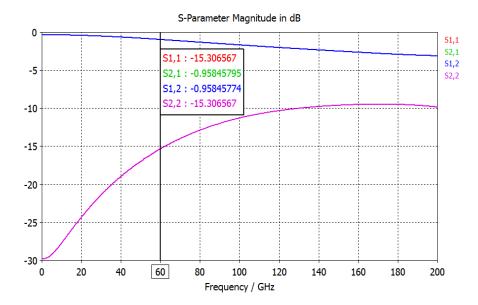

| EAM model; orange: with HBT-EAM model) 122                                                    |

| Figure 6.21: The S-parameter simulation of TWE-HBT-EAM 123                                    |

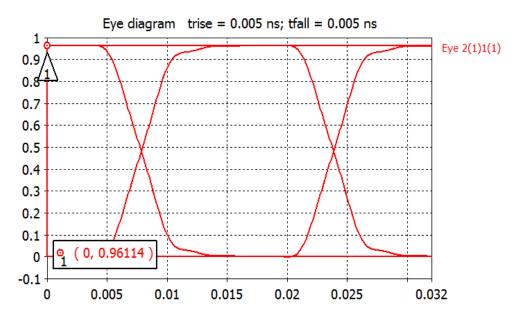

| Figure 6.22: 60Gbps Eye diagram of the HBT-based TWE-EAM 124                                  |

### List of Tables

| Table 1.1: Loss comparison of board-to-board interconnect              | 3  |

|------------------------------------------------------------------------|----|

| Table 1.2: Loss comparison of on-chip interconnect                     | 5  |

| Table 1.3: Delay comparison of board-to-board interconnect             | 6  |

| Table 1.4: Delay comparison of on-chip interconnect                    | 6  |

| Table 2.1: Depletion and Injection type modulator comparison           | 31 |

| Table 2.2: Loss Vs Vbe                                                 | 37 |

| Table 3.1: Comparison of carrier-injection modulator based transmitter | 53 |

| Table 3.2: Comparison of Figure 3.22 and Figure 3.23                   | 60 |

| Table 3.3: Comparison of Figure 3.24 and 3.25                          | 62 |

| Table 4.1: Pre-emphasis driver component values*                       | 68 |

| Table 4.2: Pre-driver component values                                 | 70 |

| Table 4.3: CML latch component values                                  | 73 |

| Table 4.4: DFF with SET function component values                      | 76 |

| Table 4.5: CML latch component values                                  | 77 |

| Table 4.6: Comparison of state-of-art low power PRBS generators        | 89 |

| Table 4.7: Transmitter performance comparison                          | 90 |

### **Chapter 1**

#### Introduction

#### 1.1 Data communication

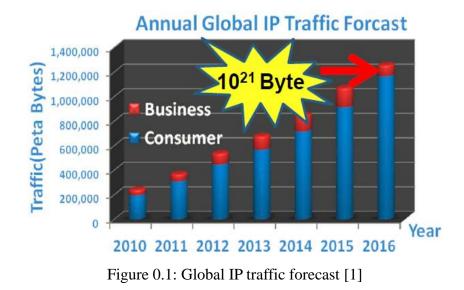

Nowadays the demand for more bandwidth is rapidly increasing driven by data intensive applications such as HD video streaming, cloud storage, etc. Varieties of internet accessible terminals such as smartphones, pads, PCs, and smart home appliances multifold the demand for data. According to the estimation by CISCO systems, in 2016 the data traffic is expected to be one zeta  $(10^{21})$  bytes, which is nearly doubled compared to 2013 as shown in Figure 1.1[1].

To keep up the pace with the data demand, scientists are keep inventing data communication methods with higher bandwidth. With unbeatable bandwidth optical interconnect is the dominant method for long distance, ultra-high speed data communication.

#### 1.2 Optical interconnect VS electrical interconnect

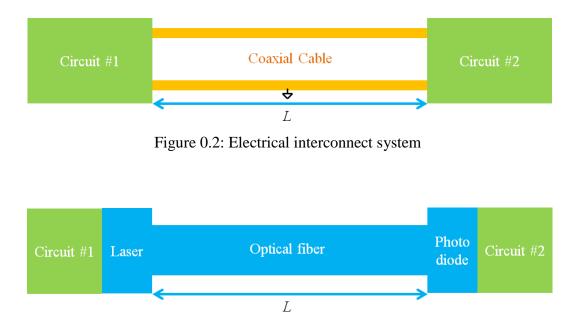

Optical fiber interconnect (or optical interconnect/link) and electrical interconnect (or electrical wire interconnect) are mainstream mediums for data communication. Base on the mediums, optical communication system and electrical communication system can be built with extra components and circuits as shown in Figure 1.2 and 1.3. In the figures the L denotes the link length. Moreover, optical interconnect requires laser (or LED) and photodiode to realize electrical-optical and optical-electrical conversion.

Figure 0.3: Optical interconnect system

Electrical interconnect mitigates the demand for extra optical component so it's favorable for short distance lower speed communication. However, due to the fact that the dielectric loss is proportional to frequency and length, electrical interconnect is not a good solution for long distance and high speed communication. Here the optical interconnect and electrical interconnect will be compared from three perspectives.

#### A. Insertion loss

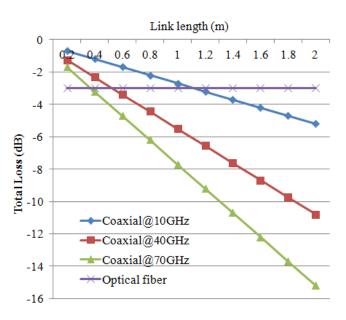

The most common board-to-board electrical interconnect is coaxial cable. The insertion loss of coaxial cable has the state-of-art specification of -7.5dB/m@70GHz[2]. On the other hand, the material loss of multi-mode optical fiber is around 0.0035dB/m[3], which means the loss from material is negligible if link length is shorter than 100m. By accounting for the coupling loss, the total loss is summarized in Table 1.1 and plotted in Figure 1.4.

|                      | Coordial apple [2] | Optical Fiber [3] |

|----------------------|--------------------|-------------------|

|                      | Coaxial cable [2]  | (multimode@850nm) |

|                      | -7.5@70GHz         |                   |

| Material loss (dB/m) | -5.3@40GHz         | 0.0035            |

|                      | -2.5@10GHz         |                   |

| Coupling loss (dB)   | -0.2               | -3                |

|                      | -0.2-7.5*L@70GHz   |                   |

| Total loss           | -0.2-5.3*L@40GHz   | -3-0.0035*L       |

|                      | -0.2-2.5*L@10GHz   |                   |

Table 0.1: Loss comparison of board-to-board interconnect

Figure 0.4: Loss comparison of board-to-board interconnect

It can be summarized that, at frequency of 10GHz, the link loss of optical fiber is less than coaxial cable when link length is longer than 1.1m; at frequency of 40GHz, the critical length is about 0.4m; while at frequency of 70GHz, the critical length is as short as 0.3m. Next generation optical fiber communication is at the speed of 50Gbps or even higher. At this data rate the electrical signal is only viable up to 10cm [4] which limits its application in the long distance communication. On the other hand, the state of art VCSEL-based optical fiber communication has been realized with data rate higher than 40Gbps [5][6][7][8].

Figure 1.5 shows supercomputer "Sequoia"[9], which has 1.5million cores and was ranked number one in the world in 2012. As it shows the communication between modules are realized by optical fiber, but not coaxial cable or other electrical wire.

Figure 0.5: Supercomputer "Sequoia" invented by IBM [9]

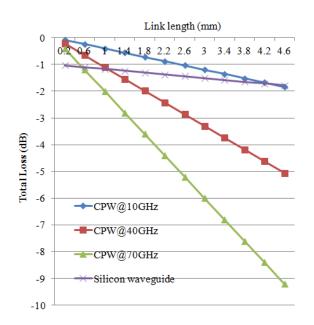

On the other hand, chip to chip to intra-chip interconnect can be realized by electrical-magnetic waveguide such as coplanar waveguide (CPW) for electrical signal or silicon waveguide for optical signal. The insertion loss of onchip CPW has the state-of-art specification of -2dB/mm@70GHz [10]. On the other hand, a state-of-art silicon optical waveguide which has the link loss of - 0.17dB/mm was proposed in [11]. By accounting the coupling loss, the total loss is summarized in Table 1.2 and plotted in Figure 1.6.

|                       | CPW [10]              | Silicon<br>waveguide[11] |

|-----------------------|-----------------------|--------------------------|

|                       | -2@70GHz              |                          |

| Material loss (dB/mm) | -1.1@40GHz            | -0.17                    |

|                       | -0.4@10GHz            |                          |

| Coupling loss (dB)    | Negligible            | -1                       |

|                       | -2* <i>L</i> @70GHz   |                          |

| Total loss            | -1.1* <i>L</i> @40GHz | -1-0.17*L                |

|                       | -0.4* <i>L</i> @10GHz |                          |

Table 0.2: Loss comparison of on-chip interconnect

Figure 0.6: Loss comparison of on-chip interconnect

It can be summarized that, at frequency of 10GHz, the critical length when link loss of optical fiber is less than coaxial cable is 4.4mm; at frequency of 40GHz, the critical length is about 0.8mm; while at frequency of 70GHz, the critical length is as short as 0.4mm. Thus, optical interconnect is favored over electrical interconnect in the application of board-to-board and intra-chip communication when the data rate is the main concern. Equalizer can be used at the receiver to retrieve the link loss for the electrical interconnect. However, it adds power consumption overhead to the system [12].

#### *B.* Propagation delay

Minimizing the signal propagation delay is a primary requirement for interconnect in very large scale integration (VLSI) architectures [13]. For ultrahigh speed interconnect the propagation delay is a critical factor for the synchronization especially when the system has many clock driven building blocks. Ideally the propagation delay should be as minimum as possible otherwise extra circuits are required for compensation which adds complexity, power budget and cost. Table 1.3 shows the unit length delay of coaxial cable and optical fiber (n=1.43). Table 1.4 shows the unit length delay of on-chip CPW and silicon optical waveguide. The optical phase velocity is defined as the phase velocity in vacuum divided by the refractive index n in the optical medium, as described by equation (1.1)

$$v = \frac{c}{n} \tag{1.1}$$

#### Table 0.3: Delay comparison of board-to-board interconnect

|              | Coaxial cable [2] | Optical Fiber [3]<br>(multimode, <i>n</i> =1.49) |

|--------------|-------------------|--------------------------------------------------|

| Delay (ns/m) | 4.43              | 4.97                                             |

|              | CPW[13] | Silicon waveguide [13]<br>(n=3.4) |

|--------------|---------|-----------------------------------|

| Delay (ns/m) | 20      | 10                                |

As the tables show, the phase delay of an optical interconnect is similar or better than an electrical interconnect. Considering the extra delay on E-O and O-E conversion components, the total delay of an optical interconnect is expected to be only one third of which of electrical interconnect in 2016 [14].

#### *C.* Power efficiency

To evaluate the power efficiency of an interconnect, a FOM is proposed as described in equation (1.2).

$$FOM = \frac{Total power of the link}{Data rate}$$

(1.2)

By using a hybrid optical I/O structure, the power efficiency is expected to reach up to 1pJ/b at data rate of 50Gbps when using a 16nm CMOS process for fabrication. On the other hand, by using monolithic optical I/O, the power efficiency is expected to be as low as 0.35pJ/b at 50Gbps data rate when using a 16nm CMOS process [12]. As discussed in [15], optical interconnect has predominant power-efficiency over electrical interconnect when interconnect length is longer than 15mm.

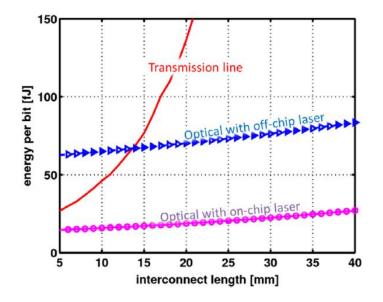

Figure 0.7: Comparison of the energy/bit of the low-latency interconnect options in a 22 nm logic node [15]

#### 1.3 Silicon photonics

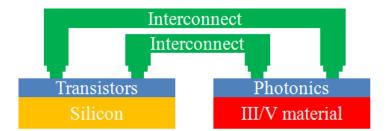

Next-generation high-performance computing systems require chip-tochip or intra-chip interconnect working at higher speed with lower loss, lower latency and higher power efficiency. The demand drives the feasibility of integration of optical communication system in the chip level. The integration can be realized by hybrid integration or monolithic integration. Hybrid integration means the optical components and electrical components are separately designed and fabricated before integrated electrically, as depicted in Figure 1.8. It has the merit that each component can be custom tailored but has the deficiency of higher cost on multi-process fabrication and chip packaging.

Figure 0.8: Hybrid integration of an OE system

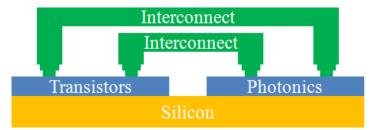

On the other hand, monolithic integration means the optical components and electrical circuits are fabricated on the same substrate as depicted in Figure 1.9. It mitigates the integration overhead, but requires traditional VLSI process compatible with optical component. The second integration method has been popularly studied recently and called photonics integrated circuits (PIC) or silicon photonics.

Figure 0.9: Monolithic integration of a OE system (silicon photonics)

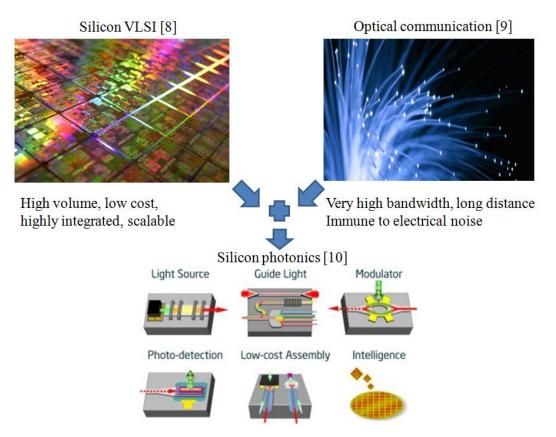

The main goal of silicon photonics is to realize optical components by using commercial silicon CMOS process. With twenty years of developing and commercialization silicon process has become the first option for large scale electronics integration with the merit of low cost, high robustness, high level integration and fast yield cycle. It becomes a main solution for most electronics realms from consumer products, such as cellular phone, WiFi, automotive radar to military products such as phase array radar. In recent years, the silicon processes are popularly studied about the possibility to be used to fabricate photonics components such as light source, waveguide, modulator, and photodetector as shown in Figure 1.10. By taking advantage of VLSI and optical communication, an unprecedented ultra-high bandwidth and high efficient interconnect can be realized within silicon chips [16][17][18]. Moreover, silicon is an attractive optical material because its transparency to infrared communication wavelengths and its high refractive index which facilitates the miniaturization of photonic devices [19]. The state of art silicon photonics optical transceiver system has the power efficiency as low as 500fJ/b [20] which utilized a commercial 40nm CMOS process for circuits fabrication and 130nm CMOS SOI platform for photonics component fabrication. The world class data rate performance of an intra-chip optical link has reached up to 25Gbps/channel [21] with power efficiency of 10.2pJ/b. By using wavelength division multiplexing technology, the multi-channel data rate can reach up to 80Gbps (4\*20Gbps)[22].

Figure 0.10: Silicon photonics [16][17][18]

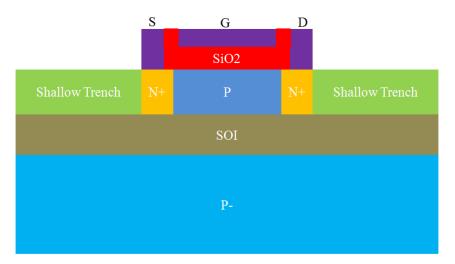

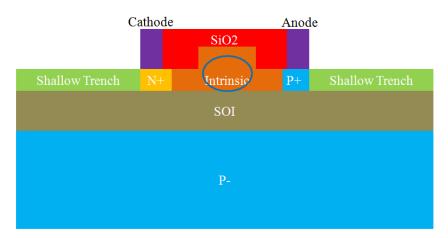

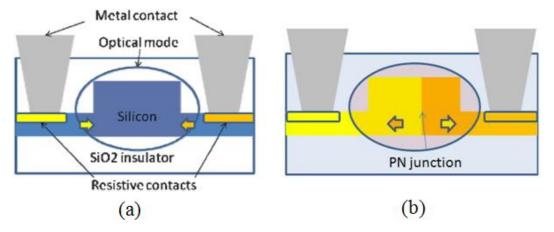

Figure 1.11 shows the cross-section view of a typical N-type MOSFET transistor in a commercial CMOS SOI process. The transistor is built on top of insulator layer and isolated by surrounding shallow trench. Figure 1.12 shows the cross-section view of an optical modulator based on P-N diode. Compared to the NMOS transistor which has N+ type doping at two terminals, the P-N diode has one N+ doped terminal and one P+ doped terminal. Same as NMOS transistor, the P-N diode has its intrinsic region covered by SiO<sub>2</sub> (could be other type of dielectric material such as Si<sub>3</sub>N<sub>4</sub>), which helps to confine the light signal in the center of the waveguide as the oval region denotes. As the figure shows from the process complexity point of view the processing modification from CMOS transistors to photonic components is cost effective. Previously deep-ultraviolet photolithography and dry-etching is popularly used for micro-fabrication of the photonics components [23]. Due to comparably high roughness which is critical to the optical signal loss, this technology is gradually replaced by E-beam

#### lithography[24].

Figure 0.11: NMOS FET in SOI process

Figure 0.12: Optical waveguide/modulator on a SOI wafer

There are some challenges to integrate the two traditionally hybrid systems onto the same substrate from the perspective of performance. For optical components, they are required to be functional at the wavelength of  $1.3\mu$ m or  $1.5\mu$ m because silicon material is "transparent" to optical signals only at those wavelengths. Secondly, the electrical-optical (EO) components need to be functional within the electrical capability of the silicon process. For example, an optical modulator which needs to be driven at 3V is not compatible with the silicon process which has the maximum rating voltage (*V*<sub>dd</sub>) of 1V.

On the other hand, the silicon processes also need to be adapted to optical components. Besides the physical layer modification described previously in Figure 1.11 and 1.12, the modification also includes the accurate modeling of optical components. Some foundries already possess the accurate modeling of some common photonics components such as imec-ePIXfab[25] while some commercial software have the co-simulation capability of electrical components and optical components such as VPIphotonics<sup>TM</sup> [26].

It's happy to see quite a few optical components have been successfully fabricated on silicon wafer in recent years, from the optical source, such as laser diode [27][28][29]; optical modulator [30]; and to photodiode [31][32]. Most existing monolithic silicon photonics systems is based on micro-ring modulator such as [33] which has merit of CMOS compatibility and ultra-low power. However, its narrow optical bandwidth and high sensitivity to temperature and process variation makes it not a robust solution. Paper [34] proposes tuning circuitry to solve this problem but it adds extra power and cost to the system. This thesis is going to present a silicon HBT modulator based optical transmitter. Besides the merit of wide optical bandwidth, the modulator has the feature of high speed, low power, low driving voltage, small footprint, high modulation efficiency which makes it a good candidate for the modulator in optical interconnect. Because the modulator is based on HBT-device in a commercial process, it can be easily monolithic integrated with VLSI circuits. In the next section, the adopted commercial process will be introduced as the background information.

#### 1.4 Silicon photonics on SiGe BiCMOS substrate

Bipolar-CMOS (BiCMOS) process is famous for the availability of high performance bipolar transistors. They are commonly used for high speed high power circuits such as power amplifier, driver circuitry, etc. Germanium (Ge) material is introduced into silicon bipolar transistors because it has a larger lattice constant and smaller energy bandgap than silicon (0.66eV vs 1.12eV), making it a suitable candidate for bandgap engineering in silicon. By introducing Ge into Si the carrier mobilities are improved with respect to pure silicon because of the reduction in carrier scattering [35] and the grading of the bandgap. The improvement of mobility will lead to high transition frequency ( $f_T$ ).

The first SiGe heterojunction bipoloar transistor (HBT) was demonstrated in 1987, and became famous in June of 1990 with the demonstration of a nonself-aligned SiGe HBT grown by ultra-high vacuum/chemical vapor deposition (UHV/CVD), with a peak  $f_T$  of 75GHz [35][36][37]. Nowadays the  $f_T$  of advanced HBT devices can reach up to 500GHz [38]. Commercialized processes such as IBM SiGe 7HP with 200nm emitter width has peak  $f_T$  of 120GHz; 8HP with 120nm emitter width has peak  $f_T$  of 210GHz; and 9HP with 90nm emitter width has peak  $f_T$  of 300GHz [39].

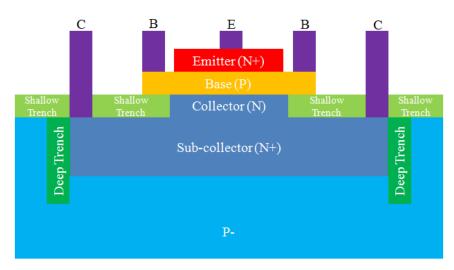

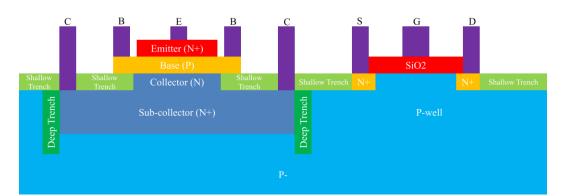

On the other hand, SiGe bipolar transistors can be easily integrated into silicon CMOS process to make a SiGe BiCMOS process. The cross-section view of SiGe HBT transistor is depicted in Figure 1.13. The germanium material is applied in gradient in the base area.

Figure 0.13: SiGe HBT device cross-section view

Figure 1.14 shows the SiGe MOSFET can be easily integrated with SiGe HBT on the same substrate. A typical state-of-art SiGe HBT BiCMOS process generally have a roughly 20% adder in mask count compared to pure digital

Figure 0.14: SiGe HBT and silicon NMOS on a same substrate

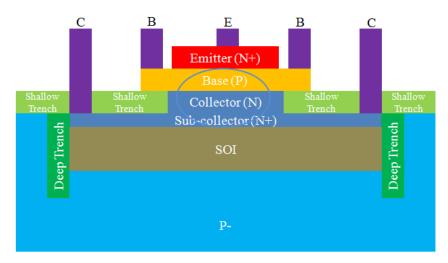

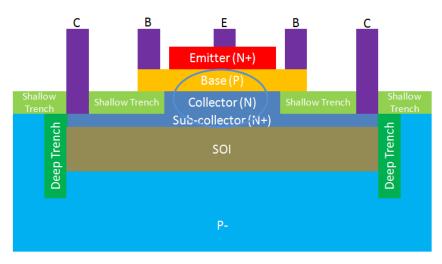

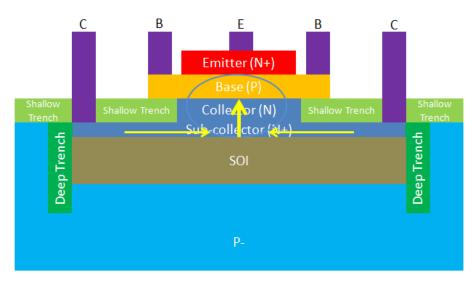

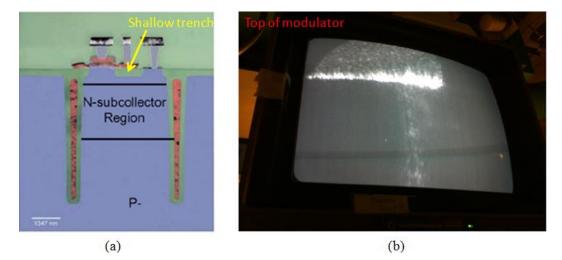

As Figure 1.13-14 shows, the existing high performance BiCMOS processes all sit on bulk silicon instead of SOI substrate for the reason of good heat dissipation because high speed HBT transistors are usually power hungry [40]. However, this stack layer configuration is not compatible with optical components. A solution for the compatibility of high performance BiCMOS process to the photonics components, which adopts a method called "local SOI" was proposed in paper [41]. Figure 1.15 depicted the method that for the HBT transistor which are used as photonics components, a SOI layer is inserted under it. The blue oval denotes the center of the light. For those HBT transistors used only for circuitry, the device structure is kept the same as Figure 1.13 shows.

Figure 0.15: Adapted photonics friendly SiGe BiCMOS process

#### 1.5 Thesis organization

This thesis is going to present a gigascale silicon photonics transmitter design integrating silicon HBT-based carrier injection electroabsorption modulator structures. The thesis is organized in the following manner. Chapter 2 will introduce the optical communication system with the focus on optical modulator. The principle, mechanism and varieties of modulator will be discussed. After that a SiGe HBT-based carrier injection electroabsorption modulator (EAM) is going to be presented from the physical design, post-processing steps to the electrical modeling and simulation results. In chapter 3 a 10Gbps driver design will be presented while the post-processing challenges and limitations will be discussed. In chapter 4 an ultra low power 6Gbps transmitter design will be discussed from the system level to every building blocks and to transistor level design. RF PCB design will be presented while measurement results from the packaged dies and chip-on-board solution will be compared. Measurement based on probe station which generates the best results will be discussed in detail. In chapter 5 a red LED-based optical communication link, which is based on the transmitter discussed in chapter 6 will be presented. It will be proved that the preemphasis can be used for LED bandwidth enhancement. In chapter 6 a traveling wave electrode design will be discussed and a new methodology will be proposed. Chapter 7 will discuss the future work of this project and the conclusion.

#### Chapter 2

#### SiGe HBT-based Carrier Injection Electroabsorption Modulator

In an optical communication system, modulator is a component used to realize electrical-to-optical signal conversion. It's a key component which significantly determines the performance of the whole system. This chapter is going to present different varieties of modulator with the focus on free-carrier dispersion effect. We are going to present a novel HBT-based carrier injection electroabsorption modulator design. Before discussing the modulator, the optical communication systems basics will be introduced, with some major specifications reviewed.

#### 2.1 Optical communication systems

#### 2.1.1 Application

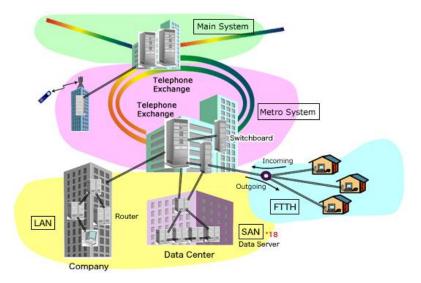

The unbeatable data rate and ultra-low loss compared to its electrical counterpart makes optical interconnect as "backbone" of global optical communications. Figure 2.1 shows an overview of optical communication systems which include main system, metro system, local area network (LAN), storage area network (SAN) and fiber to the home (FTTH) system[42]. Let's take FTTH as an example, home use internet is used to be connected by Asymmetric Digital Subscriber Line (ADSL) for many years. Because the interconnect is based on twisted wire, the physical data speed limit is about 8Mbps. With the demand for high quality experience at home such as HDTV, ADSL based internet is not a good option anymore while faster communication method is required. Thus, this field is starting to be occupied by FTTH systems. Nowadays, the

internet providers can supply personal high speed internet options such as 25Mbps, 50Mbps, 105Mbps, etc. Speed with 500Mbps is also available on the market if you would like to pay 300 dollars per month to experience the speed.

Figure 0.1: Applications of optical communication [42]

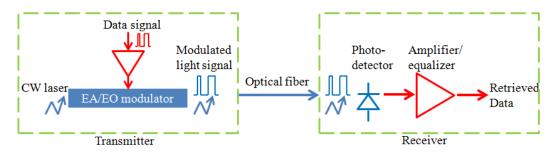

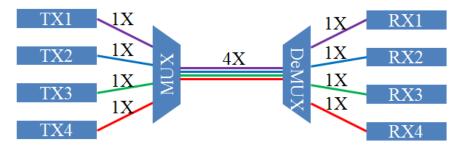

With the upgrading of the micro-fabrication and exploration of new materials, the speed of single-wavelength optical channel can reach up to 25Gbps [21]. By using wave-division-multiplexing(WDM)[43] a single optical channel can reach a speed of 50Gbps. A typical optical communication system can be described by Figure 2.2, which includes optical source, optical modulator, optical waveguide, optical detector and electrical building blocks such as modulator driver, transimpedance amplifier (TIA), limiting amplifier, equalizer, etc.

Figure 0.2: Optical communication system

#### 2.1.2 Key specifications

In this section some key specifications of an optical communication system are going to be reviewed. They will be the background information for the discussion of optical modulator.

#### *A.* Data format

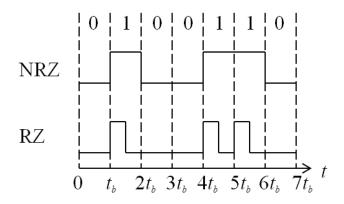

Usually, the high speed data signal is modulated on the light either by direct intensity modulation as in an electroabsorption modulator (EAM) or indirect intensity modulation as in an electro-optic modulator (EOM) represented by Mach-Zehnder interferometer (MZI). For intensity modulation the most common data format is Non-Return-Zero (NRZ) which is described by Figure 2.3. In this format the two amplitude levels representing logics zeros and ones. High level represents logic one and low level represents logic zero while the duty cycle of each bit is 100%. Return-Zero (RZ) is another format described in Figure 2.3 which has less than 50% duty cycle for logic ones and 100% duty cycle for logic zeros.

Figure 0.3: Format of NRZ and RZ signal

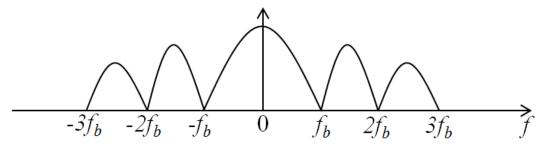

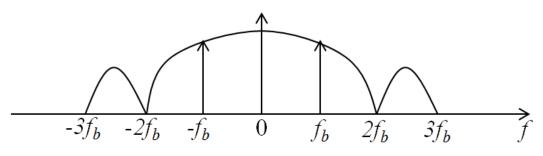

Figure 2.4 and 2.5 show the spectrum of NRZ and RZ signal respectively. In comparison, RZ signal contains clock information which provides convenience for clock recovery. However its doubled bandwidth compared to NRZ signal provides complexity to the circuit design.

Figure 0.4: Spectrum of NRZ signal

Figure 0.5: Spectrum of RZ signal

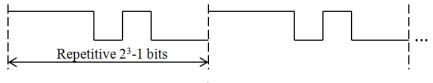

Pseudo-random bit sequence (PRBS) signal is a special data pattern used to characterize the performance of a data communication link. Because the data pattern is "random" zeros or ones which is close to the real data stream, the performance of an optical transceiver can be evaluated sufficiently by using it as a test signal. "Pseudo-random" means the sequence is not really random. Actually, it is still repetitive data pattern but only with random data sequence in each period.

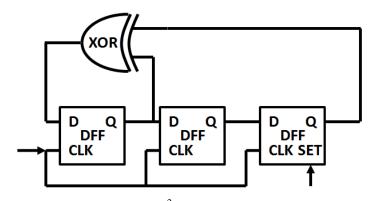

The most common PRBS generators have the data length of  $2^{3}$ -1,  $2^{7}$ -1,  $2^{15}$ -1 and  $2^{31}$ -1, etc. The longer data length means the data pattern is more complex which provides more stringent requirement for the hardware performance. A  $2^{3}$ -1 PRBS generator is shown in Figure 2.6. It consists of three DFFs triggered by the same clock signal, and one XOR gate. One of the DFFs needs to have the function to be set to logic one in order to initialize the PRBS generator while avoiding the all zero state.

Figure 0.6: 2<sup>3</sup>-1 PRBS generator

The generated bit pattern is depicted in Figure 2.7. It can be seen that the data pattern is repeated every  $2^3$ -1 bits. By using different number of DFFs the length of data pattern is different. The number of the DFFs determines the longest consecutive ones in the data pattern. For example, as Figure 2.7 shows the longest consecutive ones in a  $2^3$ -1 PRBS signal is three. The long consecutive ones/zeros is not favorable because the energy will be concentrated at DC or very low frequency which requires very wide bandwidth circuits. Otherwise, the voltage level of long consecutive ones/zeros will droop significantly.

Figure 0.7: 2<sup>3</sup>-1 PRBS signal

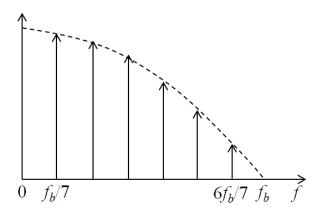

Because PRBS signal is still periodic, its spectrum is a bunch of tones with the spacing of 1/( bit length\*bit duration). The envelope of the tones is the same as NRZ signal as shown in Figure 2.4. Figure 2.8 depicts the spectrum of the  $2^3$ -1 PRBS signal with the tone spacing of 1/(7\*bit duration). The spectrum beyond  $f_b$ is not shown here for simplicity but it has the same tone spacing and the envelope as Figure 2.4 with zeros at integers of  $f_b$ .

Figure 0.8: spectrum of PRBS signal

#### B. Eye diagram

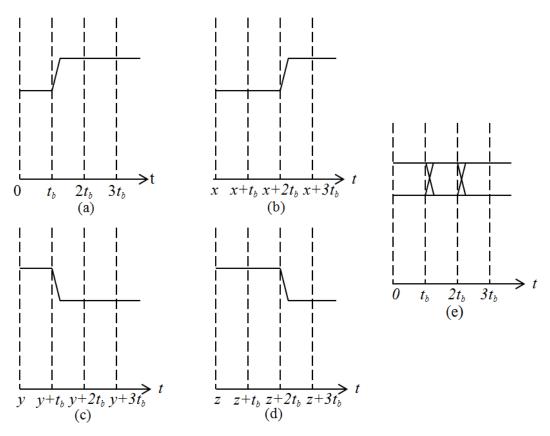

For a data signal the most important specifications are: the amplitude of logic ones and zeros; the rise/fall time at logic transitions; and the timing of each bit. All those information can be achieved by overlapping each bit on top of each other and display them in a small time window, which is called "eye diagram". There are a lot of information can be retrieved from eye diagram, such as the bandwidth, noise, etc. Figure 2.9 describes an example of how an eye diagram is formed by separate bits. Here  $t_b$  denotes the time duration of each bit. Figure 2.9(a) shows three bits at time from 0 to  $3t_b$  with a logic zero to one transition at  $t_b$ . Figure 2.9(b) shows three bits at time from x to  $x+3t_b$  with a logic zero to one transition at  $x+2t_b$ . Figure 2.9(c) shows three bits at time z to  $z+3t_b$  with a logic one to zero transition at  $z+2t_b$ . Figure 2.9(d) shows three bits at time z to  $z+3t_b$  with a logic one to zero transition at  $z+2t_b$ . Figure 2.9(a), which forms the eye diagram.

Figure 0.9: how an eye diagram formed

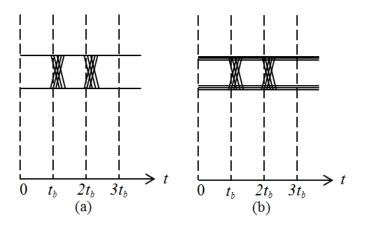

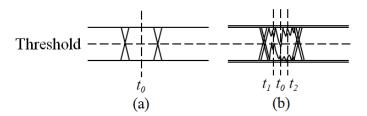

While Figure 2.9(e) shows the ideal eye diagram, Figure 2.10 shows an example of realistic eye diagram. Figure 2.10(a) depicts the problem that every logic transition is not overlapping each other perfectly but with some variations. The accumulation of the variations is called peak-to-peak jitter ( $J_{pp}$ ), which is usually due to the noise of circuits, or the circuits are data pattern dependent.

#### Figure 0.10: (a) Jitter and (b) noise

Figure 2.10(b) depicts the non-ideality of amplitude, which makes a smaller eye opening than the ideal eye diagram. This problem is mainly due to the circuit noise or the DC droop caused by circuit limited bandwidth, and it may cause the decision circuits to make errors.

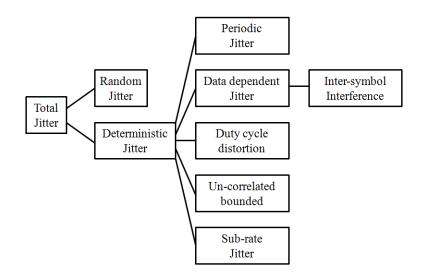

There are several different jitter definitions. Peak-to-peak jitter  $J_{pp}$  and root-mean-square (rms) jitter  $J_{rms}$  are two commonly used jitter specifications. Jitter can be decomposed into different categories. Figure 2.11 shows jitter is composed of random jitter and deterministic jitter, while the deterministic jitter can be further decomposed to period jitter, data dependent jitter, etc. Nowadays advanced sampling oscilloscopes have the capability to do these jitter analysis.

Figure 0.11: Jitter components

### C. Bit error rate

Both noise and inaccurate timing could generate logic error. Figure 2.12(a) shows the ideal timing which is at the center of each bit while the bit is clean without noise. Figure 2.12(b) shows a realistic eye which carries a lot of noise while the timing could vary from  $t_1$  to  $t_2$ . The decision circuit will generate a logic error if the sampling is at  $t_1$  or  $t_0$  but error free if it is at  $t_2$ .

Figure 0.12: Logic error

Bit error rate (BER) is the specification used to describe how many logic errors happen in an amount of bits. Usually the claimed data rate of an optical system is described based on a specific BER, such as 10<sup>-12</sup>, which means the system has only one bit error after sending one trillion bits at the claimed data rate. The BER is directly related to the signal to noise ratio (SNR), which can be statistically described by equation (2.1, 2.2) [44][45].

$$SNR = \frac{eye \ level \ one-eye \ level \ zero}{rms \ noise \ level \ one+rms \ noise \ level \ zero}$$

(2.1)

$$BER \approx \frac{1}{SNR^*\sqrt{2\pi}} e^{\frac{-SNR^2}{2}}$$

(2.2)

### D. Bit rate

Bit rate is a major specification of every data communication method because it is a specification that end consumer can really feel directly and care most. Bit rate is determined by almost every building block in the system. On one hand, the component which has lowest bandwidth in the system determines the maximum bit rate of the system. On the other hand, the noise contribution of every building block and the loss of the link medium decrease the SNR and the bit rate at a specific BER.

The state of art bit rate performance of single wavelength can reach up to 25Gbps per channel. The bit rate can be multi-folded by using Wavelength Division Multiplexing (WDM) which is described in Figure 2.13. By using comb laser, the data rate in a single optical waveguide can be increased by four times.

Figure 0.13: WDM transceiver system

## *E.* Link power budget

Power efficiency is an important specification for battery powered systems. Although most optical communication system is not battery powered, there are some exceptions. For example, some optical interconnects which are used to replace the traditional electrical interconnects have stringent power budget because they need to defeat the electrical interconnects from every perspective. The power efficiency of an optical interconnect is evaluated by the required energy to send a single bit depicted by the unit of pico-joule-per-bit (pJ/b).

With stringent budget, every component in the optical link needs to be upgraded or improved. The state of art low power optical link has the power efficiency around 1pJ/b[12].

## F. Cost

Although cost is not the most important specification in front of many other obstacles, it will be definitely an important one when silicon photonics technology becomes more mature and commercialized. There are some agencies which can provide standard silicon photonics components fabrication and fast production cycle, such as OPSIS; It can be predicted that, similar to silicon VLSI circuits technology, the cost of silicon photonics will keep reducing in the near future while it becomes more and more mature and commercialized.

### 2.2 Optical modulator

In an optical transmitter, modulator is a component used to realize

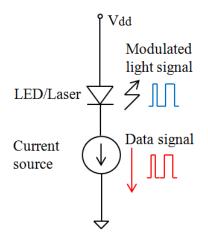

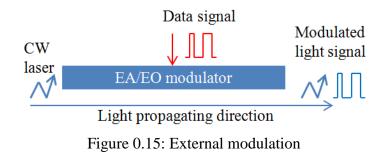

electrical-to-optical signal conversion. It's a key component which performance significantly determines the performance of the whole optical link. Usually, optical modulator is driven by electrical signal. The modulation of an optical signal can be realized by internal modulation, i.e. switching on and off the LED/laser directly by using a data modulated current source as depicted in Figure 2.14; or by external modulation, i.e. using fast switched optical modulator to modulate a continuous wave light source, as depicted in Figure 2.15. Usually internal modulation is not as efficient as external modulation. Most multi-Gbps optical modulator adopts the external modulation method. This section will focus on the external modulator and its ramifications.

Figure 0.14: Internal modulation

#### 2.2.1 Free carrier plasma effect

External optical modulator can be sorted into several categories by its modulation mechanism. The first category Electro-optic (EO) modulator relies on

the refractive index change brought by the external electrical field change as described in equation (2.3). The linear term of the Taylor expansion is defined as Pockels effect and the second order term is defined as Kerr effect. Traditional  $L_iN_bO_3$  based optical modulator adopts the Pockels effect, thus they have very linear n(E) relationship.

$$n' = n + a_1 E + a_2 E^2 + \cdots$$

(2.3)

Unfortunately, silicon has very weak Pockels or Kerr effect. Most silicon EO modulators utilize the free carrier plasma effect to manipulate the refractive index. The free carrier plasma effect is the second modulator mechanism category which refers to the change of refractive index manipulated by the change of electron and hole densities. As illustrated by Drude [46], the change of real part of refractive index,  $\Delta n$ , and change of imaginary part of refractive index,  $\Delta \alpha$ , are determined by the electron and hole density change,  $\Delta N_e$  and  $\Delta N_h$ . Soref derived an empirical equation for free carrier plasma effect in silicon, as described in equation (2.4)[47]

$$\begin{cases} \Delta n = \Delta n_e + \Delta n_h = -[8.8 \times 10^{-22} \Delta N_e + 8.5 \times 10^{-18} \Delta N_h^{0.8}] \\ \Delta \alpha = \Delta \alpha_e + \Delta \alpha_h = 8.5 \times 10^{-28} \Delta N_e + 6 \times 10^{-18} \Delta N_h \end{cases}$$

(2.4)

In the meanwhile, silicon is an attractive optical material from two perspectives. Firstly, it is transparent to infrared communication wavelengths. And secondly its high refractive index facilitates the miniaturization of photonic devices [48].

#### 2.2.2 Silicon modulator varieties

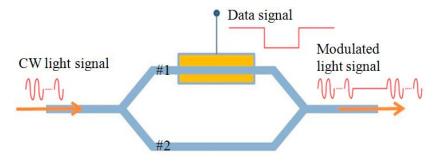

By taking advantage of free carrier dispersion effect in silicon, there are three main categories of modulators. The first category is represented by Mach-Zehnder Interferometer (MZI) which uses phase change to realize amplitude modulation. The mechanism is described by Figure 2.16. The continuous wave light enters into a MZI and splits into two branches. Branch #2 is free of modulation signal with the light phase at the output of MZI shifted by *x* degree. Branch #1 is modulated by a high frequency data signal which changes the light phase by  $x+\pi$  degree with an extra of  $\pi$  degree compared to branch #1. At the output of the MZI, the light signals of the two branches are either constructively added which generates logic one, or destructively added which generates logic zero. For MZI,  $V_{\pi}L_{\pi}$  is a FOM describing the modulation efficiency. Here  $L_{\pi}$  denotes the length of modulator which achieves the extra phase shift of  $\pi$  while  $V_{\pi}$  denotes the required AC voltage swing.

Figure 0.16: Mach-Zehnder Interferometer

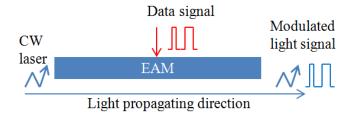

The second category is called electroabsorption modulator (EAM). Different from MZI, it takes advantage of the light intensity change but not the phase change to realize the modulation. As depicted in Figure 2.17 the EAM has only one optical channel. The electrical data signal modulates the absorption coefficient of the waveguide, which will translate to the light strength change at the output of modulator waveguide. The difference of the light strength represents logic ones and zeros. In essence, EAM is working as an electrical controlled optical switch.

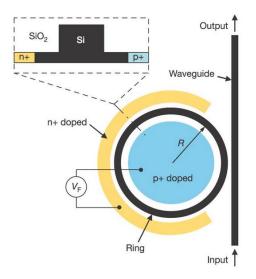

The third category of silicon modulator adopts resonant structure such as micro-ring modulator as showed in Figure 2.18[8]. The light is absorbed into the resonant cavity when the ring is not-biased, or path through the waveguide when the ring is forward-biased. The light intensity change at the output of the waveguide represents the logic zeros and ones.

Figure 0.18: Micro-ring modulator [49]

Waveguide based modulators such as EAM or Mach–Zehnder modulators have the benefit of wideband operation, and hence greatly reduced the temperature sensitivity. Resonant structures greatly enhance the relatively weak free-carrier effect, thereby enabling ultra-low power consumption [50]. Moreover, it has the merits of CMOS process compatibility and low driving voltage. However, it has the deficiency of very narrow optical bandwidth which is highly sensitive to temperature and process variation.

### 2.2.3 Carrier injection VS Carrier depletion

The free carrier dispersion effect can be mainly utilized by two different methods. Modulator that change the carrier density based on majority carrier movement through the depletion region is classified as depletion type as shown in Figure 2.19(a)[19]; while the modulator that change the carrier density by minority carrier injection through a p-n junction is classified as injection type as shown in Figure 2.19(b).

Figure 0.19: Modulator types (a) injection (b) depletion [19]

Both depletion and injection modulators have their merits and deficiencies. Firstly, from the speed perspective the depletion modulators are intrinsically faster than injection modulators because their moving carrier is majority carrier. Secondly, from the perspective of CMOS process compatibility the injection modulators are favorable because the required driving voltage can be 1V or even lower; while the required driving voltage for depletion modulators is usually 3V or higher, which hinders their integration with advanced commercial silicon processes. Thirdly, depletion modulators have better linearity which provides design convenience for high speed drivers. Fourthly, injection modulators intrinsically have much higher free carrier density change, which means the required footprint is much smaller. The low driving voltage and small footprint both lead to better modulation efficiency for injection modulators. Table 2.1 summaries the specifications comparison of depletion or injection modulators.

|                       | Carrier depletion | Carrier injection |

|-----------------------|-------------------|-------------------|

| Bias type             | Reverse           | Forward           |

| Bias voltage          | High              | Low               |

| Linearity             | Very good         | Weak              |

| Footprint             | Large             | Compact           |

| Modulation efficiency | Low               | High              |

| CMOS compatibility    | Weak              | Good              |

Table 0.1: Depletion and Injection type modulator comparison

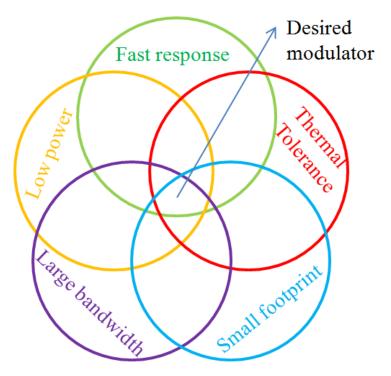

### 2.2.4 Ideal modulator

There are five major features a modulator should possess: fast response; low power; wide optical bandwidth; small footprint; and thermal tolerance. Unfortunately these features compromise to each other. For example, depletion modulators usually have fast response because the moving carrier is majority; however, the majority carrier density is low which leads to large device footprint requirement. Figure 2.20 defines the features of an "ideal modulator", which are the design targets for an optical modulator.

Figure 0.20: Desired modulator features

## 2.3 SiGe HBT-based Carrier Injection Electroabsorption Modulator

HBT device is a breakthrough innovation for ultra-high speed circuits and systems for its unbeatable gain at high frequency compared to MOSFET. Nowadays the HBT device in commercial BiCMOS process has the transition frequency  $f_T$  as high as 200-300GHz. Traditionally, people use pn, p-i-n diodes to realize a optical modulator. In 2009, a group at RPI firstly presented a high speed modulator design based on a HBT device[51]. Based on the device, some researchers have proposed modification and huge improvement which leads to a simulated speed of 80Gbps or more [52][53][54]. This section is going to introduce a newly developed HBT-based modulator design working in the carrier injection mode, which has the merits of high speed, low power, small footprint and wide optical bandwidth.

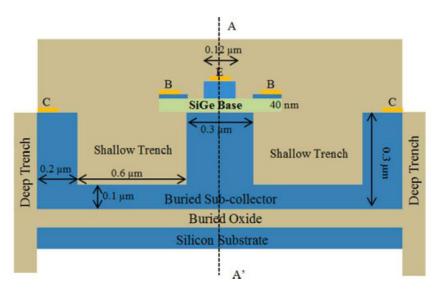

### 2.3.1 Device structure

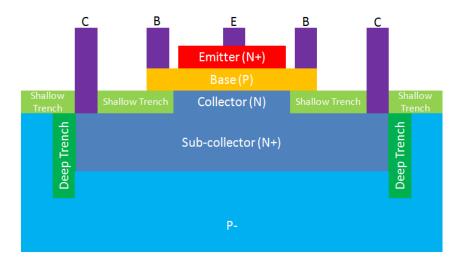

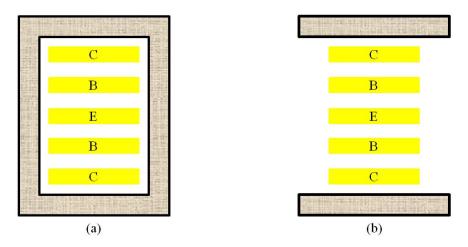

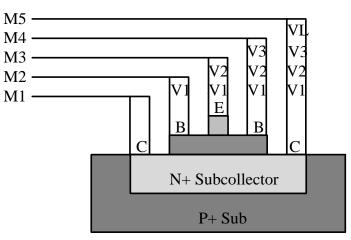

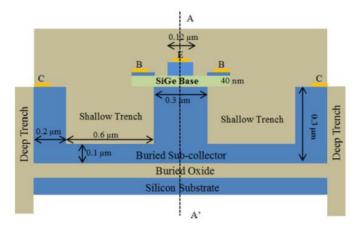

Standard HBT device in a commercial BiCMOS process is depicted in

Figure 2.21. It has two base and two collector contacts and one emitter contact. The symmetrical structure is for better speed and reliability performance. It has deep trench isolating every single HBT device for less coupling, and shallow trench at non-active region for better isolation among the three terminals in a single HBT device. The key of high  $f_T$  is the small emitter width which is 120nm, and the small base thickness which is 40nm for this process. Different from SOI process, BiCMOS process is not designed sitting on a insulator layer due to heat dissipation problem because HBT devices are usually power hungry[35]. This feature requires an extra post-processing step to make it a good optical waveguide.

Figure 0.21: HBT-device in a SiGe BiCMOS process

Figure 2.22 depicts the structure of a desired HBT-based modulator. As it shows an insulator layer is sitting under the HBT device which helps to form a optical waveguide and push the center of the light into the base region where the free carrier density change is significant.

Figure 0.22: Idea of a HBT-based optical modulator

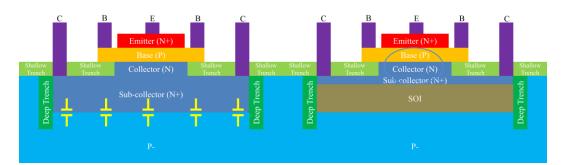

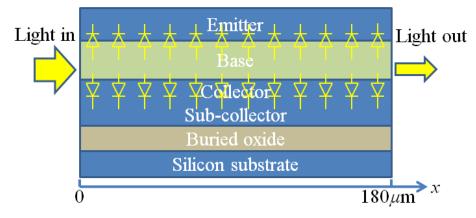

Our collaborators at Rensselaer Polytechnic Institute designed a HBTbased modulator device shown in Figure 2.23 with all the dimensions depicted [55]. The modulator is designed as the similar as possible to the HBT device in IBM SiGe BiCMOS 8HP process based on accessible information from the process design kit (PDK).

Figure 0.23: Designed HBT-based optical modulator with dimensions [55]

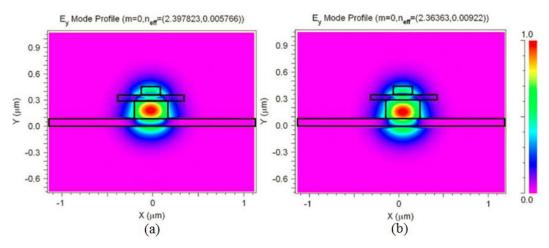

### 2.3.2 Optical property

The carrier distribution of this device under the "on" and "off" state is

simulated by using Synopsys Sentaurus. Based on the carrier distribution, the refractive index can be calculated by using Soref's equation. Then the optical property is simulated by the Beam Propagation Method (BPM) module in Rsoft and the optical field of Transverse Magnetic (TM) polarization can be achieved which is shown in Figure 2.24. As it shows the optical signal is mainly sitting in the base and subcollector region, which requires large carrier density change in this region in order to get good modulation efficiency.

Figure 0.24: (a) TM mode OFF state, (b) TM mode ON state [55]

### 2.3.3 Speed

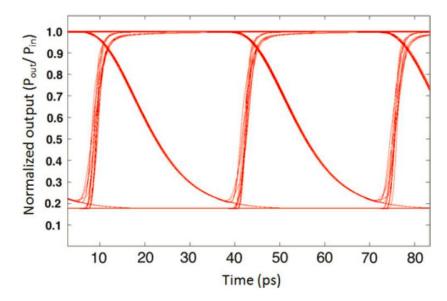

For a carrier injection modulator, the switching speed is determined by the speed of carriers injected into the intrinsic region and the speed of carriers swiped out from the intrinsic region to the ground. The intrinsic switching speed of the HBT modulator is around 30Gbps as described by Figure 2.25. It should be noted that the results are achieved under the condition of ideal driver circuit. The "Ideal" driver means the driver has zero output impedance while the driving signal has infinite short rise/fall time.

Figure 0.25: Transient response of HBT modulator [55]

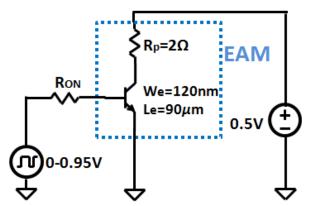

For a carrier-injection HBT modulator, the small output impedance of a realistic driver circuit is a critical requirement to achieve a large base-emitter voltage swing  $V_{be}$ , which affects the extinction ratio; and to minimize charging/discharging time to achieve high data rates. Thus the performance of driver circuit determines whether the modulator's claimed performance can be achieved or not. Furthermore, there are some commonly used techniques to enhance the modulator's claimed bandwidth from the perspective of driver. Pre-emphasis is a common method to increase the speed of modulator without changing the design of modulator.

## 2.3.4 Extinction ratio

The HBT-based modulator can be either worked as an EOM in a MZI or as an as an EAM. EAM is mainly discussed here because it is easier to be implemented. The extinction ratio of an EAM is determined by the magnitude of the extra loss when a external electrical field is applied. The unit length loss without external electrical field (or called device intrinsic loss) is about  $0.183dB/\mu m$ . By applying forward bias voltage of 0.95V cross B-E junction, the unit loss becomes  $0.213dB/\mu m$ . The extra loss  $0.03dB/\mu m$  will accumulate along the modulator and determine the extinction ratio at the output of the modulator. Table 2.2 summaries the unit length loss under different forward bias voltage  $V_{be}$ . The relationship between absorption coefficient  $\alpha$  and unit length loss can be described by equation (2.5). It can be seen from the Table 2.2 that, if  $V_{be}$  is switching between 0.1V and 0.95V, the extinction ratio of this modulator with 180 $\mu$ m length is (0.213-0.183)\*180=5.4dB. And the insertion loss is 0.183\*180=32.94dB.

$$Loss = \frac{\alpha * 4\pi * 10}{ln(10) * 1.55} \qquad (dB/\mu m)$$

(2.5)

| $V_{be}$ | ∆n imag  | α        | $L_{\pi}(\mu m)$ | $Loss(dB/\mu m)$ |

|----------|----------|----------|------------------|------------------|

| 0.01     |          | 0.005208 |                  | 0.183377396      |

| 0.1      | 8E-06    | 0.00522  | 96875            | 0.183805581      |

| 0.2      | 1.7E-05  | 0.005231 | 45588.24         | 0.184176675      |

| 0.3      | 2.9E-05  | 0.005232 | 26724.14         | 0.184233766      |

| 0.4      | 4.7E-05  | 0.00524  | 16489.36         | 0.184490677      |

| 0.5      | 6.9E-05  | 0.005267 | 11231.88         | 0.18546123       |

| 0.6      | 9.6E-05  | 0.00527  | 8072.917         | 0.185546867      |

| 0.7      | 0.000126 | 0.005299 | 6150.794         | 0.186574511      |

| 0.8      | 0.000186 | 0.005322 | 4166.667         | 0.18737379       |

| 0.85     | 0.000275 | 0.005365 | 2818.182         | 0.188886711      |

| 0.9      | 0.000634 | 0.005549 | 1222.397         | 0.195366578      |

| 0.91     | 0.000792 | 0.005635 | 978.5354         | 0.198392419      |

| 0.92     | 0.000967 | 0.005722 | 801.4478         | 0.201475352      |

| 0.93     | 0.001154 | 0.005836 | 671.5771         | 0.205500292      |

| 0.94     | 0.001351 | 0.005948 | 573.6491         | 0.209411049      |

| 0.95     | 0.001557 | 0.006076 | 497.7521         | 0.21394981       |

| 0.96     | 0.00177  | 0.0062   | 437.853          | 0.21837439       |

| 0.97     | 0.001989 | 0.00634  | 389.643          | 0.223341336      |

| 0.98     | 0.002212 | 0.00648  | 350.362          | 0.228165555      |

| 0.99     | 0.002439 | 0.00662  | 317.753          | 0.233103956      |

| 1        | 0.002669 | 0.00678  | 290.371          | 0.238641817      |

| 1.01     | 0.002899 | 0.00692  | 267.334          | 0.243751492      |

| 1.02     | 0.003131 | 0.00708  | 247.525          | 0.249146624      |

| 1.03     | 0.003363 | 0.00723  | 230.449          | 0.254456119      |

| 1.04     | 0.003594 | 0.00737  | 215.637          | 0.259537248      |

| 1.05     | 0.003824 | 0.00753  | 202.667          | 0.265246383      |

Table 0.2: Loss Vs Vbe

| 1.06 | 0.004055 | 0.00768 | 191.122 | 0.270527332 |

|------|----------|---------|---------|-------------|

| 1.07 | 0.004285 | 0.00784 | 180.863 | 0.275979555 |

| 1.08 | 0.004516 | 0.00799 | 171.612 | 0.28148887  |

| 1.09 | 0.004746 | 0.00815 | 163.295 | 0.286884002 |

| 1.1  | 0.004975 | 0.0083  | 155.779 | 0.29230768  |

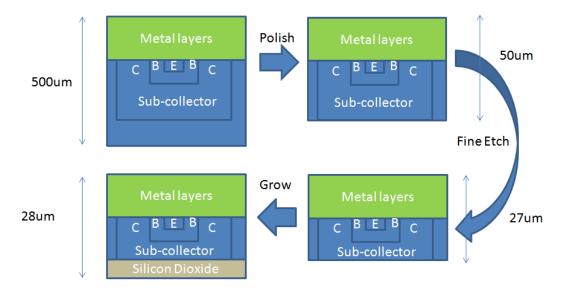

### 2.3.5 Fabrication

The first step of fabrication is through commercial foundry. By taking advantage of their comprehensive fabrication facility, the HBT structure with  $0.12\mu$ m feature size is nicely fabricated. After the device is back from foundry there are several necessary post-processing steps need to be finished on the device as shown in Figure 2.26. Firstly, the die substrate is polished from 500 $\mu$ m down to 50 $\mu$ m. Then the substrate is fine etched to 27 $\mu$ m, which makes the subcollector thickness down to 0.1 $\mu$ m as designed. After that an oxide layer with 1 $\mu$ m thickness is grown on the backside of the device. Before polishing and etching, a cladding layer is attached on top of the die to avoid breaking.

Figure 0.26: Post-processing steps

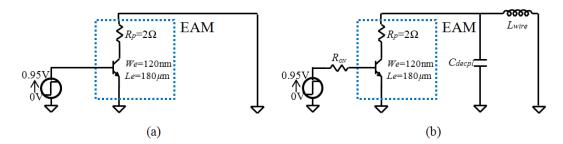

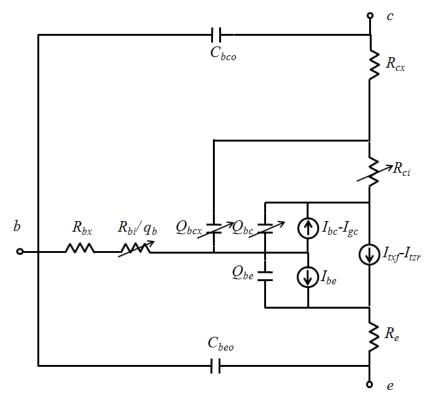

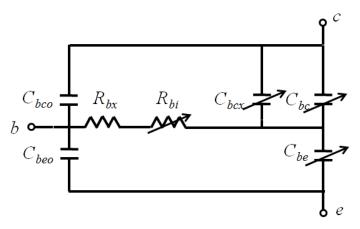

### 2.3.6 Electrical Model

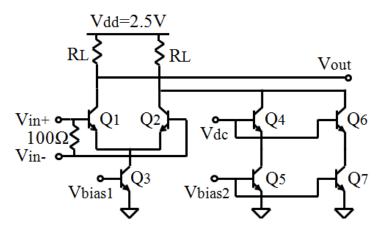

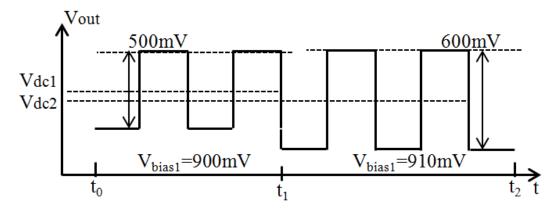

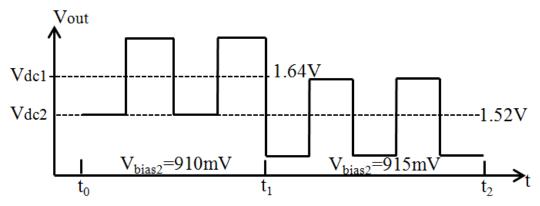

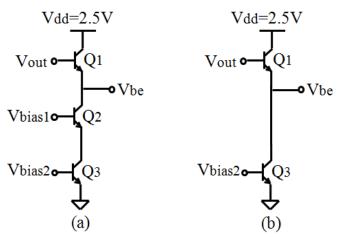

Post-processing steps introduce several modifications to the standard electrical model provided by the foundry. The first modification is, the thinner