# Thermal Demonstration of High Density Processor Packages

Submitted By Peter Houghton Lewis

### IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

## **BACHELOR OF SCIENCE IN MECHANICAL ENGINEERING**

School of Engineering Tufts University Medford, Massachusetts

May 2014

Signature of Author: Peter Houghton Lewis Certified By: Associate Professor Robert D. White Department of Mechanical Engineering Tufts University

Committee: Associate Professor Robert D. White Department of Mechanical Engineering Tufts University Committee: Dr. Brian Smith Draper Laboratory

## Abstract

As technology continues to miniaturize processor chips, the thermal load of the electronics has become a primary hindrance in the development and implementation of more powerful chips. An internal effort by Draper Laboratory has been made in order to characterize the effect of their high density packaging method on the thermal load. The following thesis provides a thermal characterization of Draper Laboratory's integrated Ultra-High Density (iUHD) material, an extreme miniaturization packaging method. The thesis covers the thermal effects of multiple layers of the iUHD material, the presence of metal traces, the isolation of the testing module's components and the stacking of multiple modules. The thermal contribution of a layer of the iUHD material was determined to be 0.067-0.077 °C/W depending on the number of layers and the presence of metal traces. The thermal resistance contribution of the components of the second layer of the stack was determined to be 0.24 °C/W. The isolation of module components was successful and locally raised the temperature in the isolated areas by 4-5 times.

# Acknowledgements

I would like to thank Brian Smith for mentoring me through the project and always making the time to meet with me to discuss the experiments. His patience and enthusiasm were infectious, making the project always interesting. I would also like to thank John Burns for the time he spent on various aspects of the project including the laser drilling of the shadow mask for the fabrication of the stack. Doug Gaither was an incredible help, always willing to talk things over or help me find any materials I needed for the research. On the fabrication side of things I would like to thank Dan Frigon and Bill Teynor for taking the time to work with me. Last, I would like to thank Cappy who did much of the background work on the project and whose assistance made the Labview integration work as well as it did.

# **Table of Contents**

| Chapter 1: Introduction                                   | 8  |

|-----------------------------------------------------------|----|

| 1.1 Problems to be Addressed/Significance                 | 8  |

| 1.2 Relevant literature                                   | 9  |

| Chapter 2: Design                                         |    |

| 2.1 Mathematical Theory of the Thermal Resistance Network | 13 |

| 2.2 Module Fabrication                                    | 19 |

| 2.3 Electrical Design                                     | 25 |

| 2.4 Design of Module Testing Stand                        | 29 |

| Chapter 3: Experimental Results                           |    |

| 3.1 Results of Diode and Heater Calibration               | 35 |

| 3.2 Results from Modules with Differing Layers            |    |

| 3.3 Results of Heater Isolation                           | 40 |

| 3.4 Results of Module Stack                               | 44 |

| Chapter 4: Conclusions                                    |    |

| 4.1 Contributions to Field                                | 48 |

| 4.2 Future work                                           | 48 |

| References                                                | 51 |

| Appendix                                                  | 53 |

| A.1 Individual Diode and Heater Calibration               | 53 |

| A.2 Labview Data-Interpretation Program Design            | 56 |

| A.3 Fabrication of Stack                                  | 61 |

| A.4 Error Analysis                                        | 66 |

| A.5 Thermal Test Data                                     | 68 |

|                                                           |    |

### **Table of Figures**

| Figure 1: Diagram of difference between typical a high power chip and Draper's embodiment [1]8                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

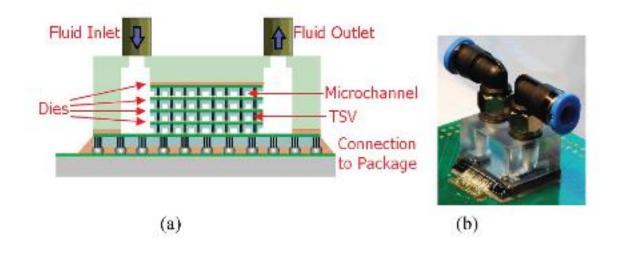

| Figure 2: Manufactured prototype and cross section of a test stack with interlayer liquid cooling. (a)<br>Cross Section [5] (b) Prototype [6]10                                                                      |

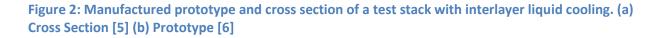

| Figure 3: High-Density Multichip Interconnect Modules: Three generations of Hughes packaging technology [8]                                                                                                          |

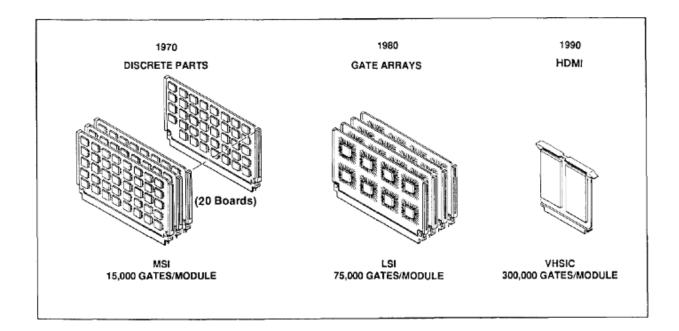

| Figure 4: Thermal module cross-section [1]14                                                                                                                                                                         |

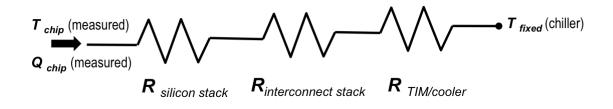

| Figure 5: Thermal resistance path for testing module [10]15                                                                                                                                                          |

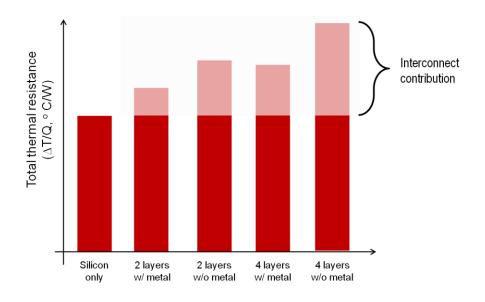

| Figure 6: Theoretical contribution of interconnect layers [10]18                                                                                                                                                     |

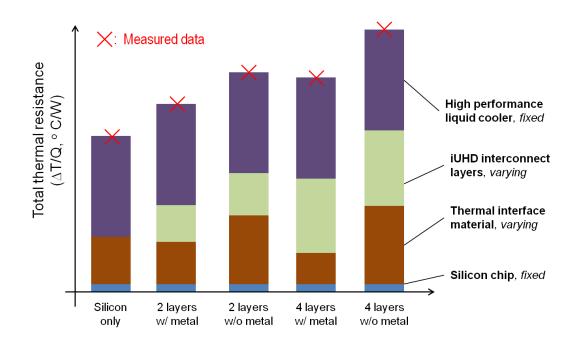

| Figure 7: In reality interconnect layers vary along with TIM thickness [10]                                                                                                                                          |

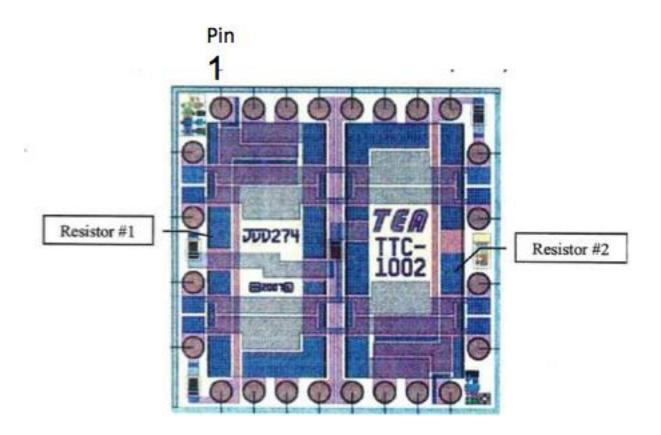

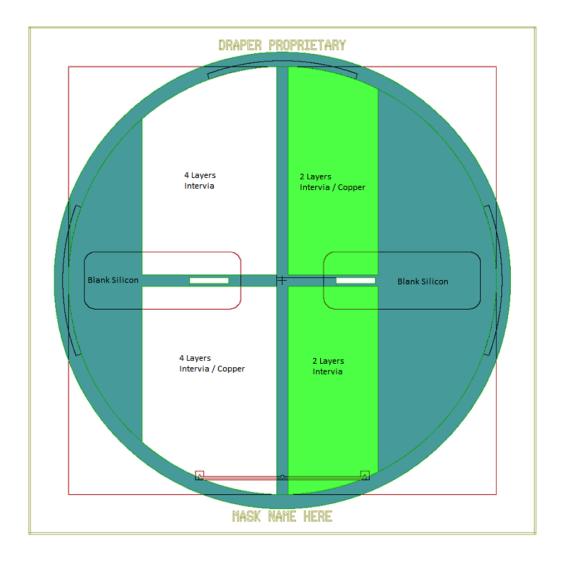

| Figure 8: Top View of chip produced by TEA Inc20                                                                                                                                                                     |

| Figure 9: Embodiment of thermal testing stack up [1]21                                                                                                                                                               |

| Figure 10: Schematic of the backside of the wafer post-processing created by John Burns IV [11]22                                                                                                                    |

| Figure 11: High-level process flow for chip fabrication created by John Burns IV. [11]                                                                                                                               |

| Figure 12: Two diodes with the heaters wired together such that one switch turns on the heater for both chips [1]                                                                                                    |

| Figure 13: Thermal picture of module with all the heaters on with a surface temperature of 98.09°C29                                                                                                                 |

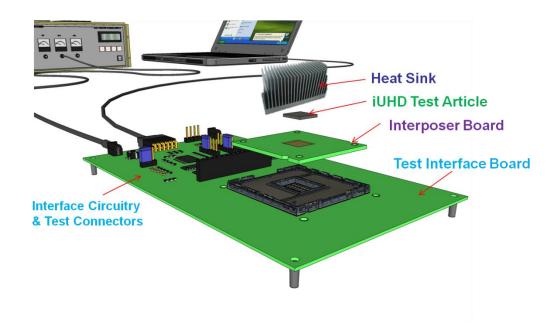

| Figure 14: Thermal Test Stand29                                                                                                                                                                                      |

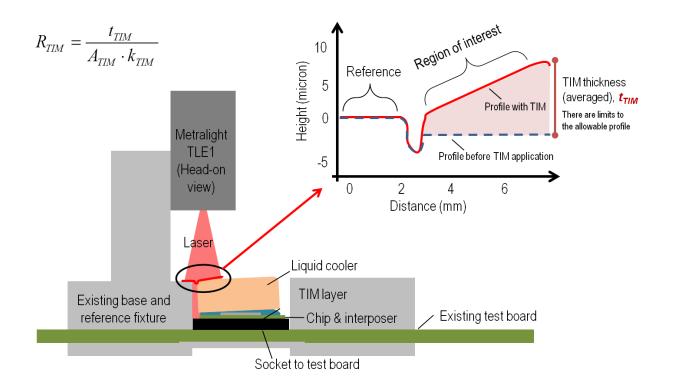

| Figure 15: Graphic showing use of Metralight Triangulation Laser [10]                                                                                                                                                |

| Figure 16: The mapping of heater switches to the module surface. The left diagram represents the heater switches and the right diagram represents the corresponding heater locations looking down at the module face |

| Figure 17: Overview of testing apparatus32                                                                                                                                                                           |

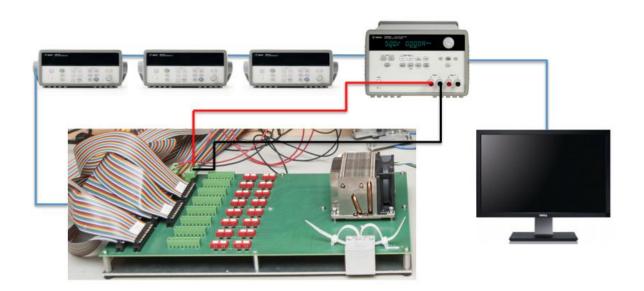

| Figure 18: The latching mechanism clamps down around the edges of the module creating an electrical path between the module and the PCB                                                                              |

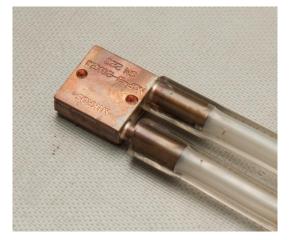

| Figure 19: The liquid cooled heat sink used on the thermal test stand                                                                                                                                                |

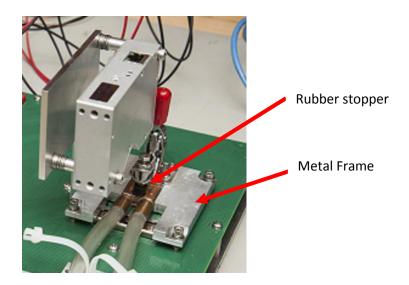

| Figure 20: Components of the module attachment to the thermal test stand are shown above. The rubber stopper and the metal frame secure the cooler during testing                                                    |

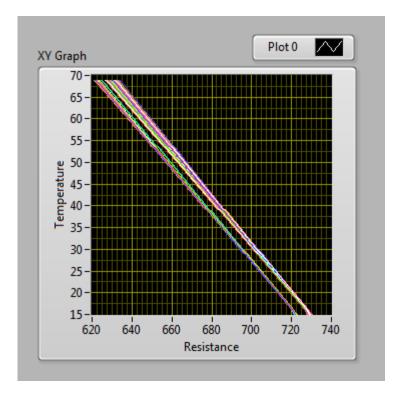

| Figure 21: Calibration plot for the 64 diodes of one of the modules. Each diode has a specific calil line. Each module has a similar looking plot                                              |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

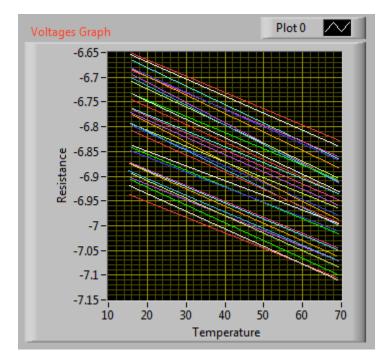

| Figure 22: Calibration plot for the 32 heaters of one of the modules. Each heater has a specific calibration line. Each module has a similar looking plot                                      |    |

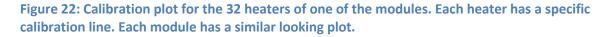

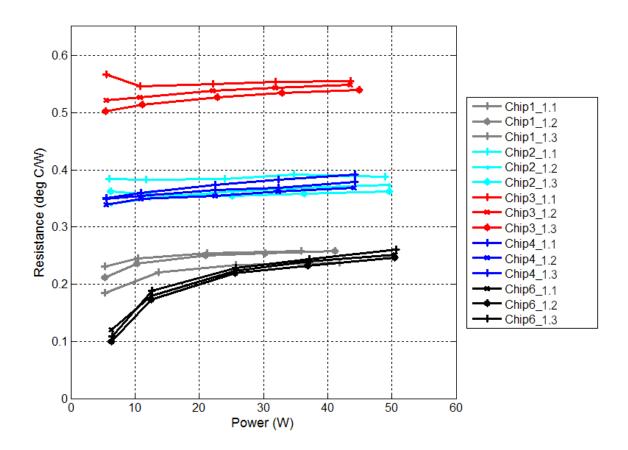

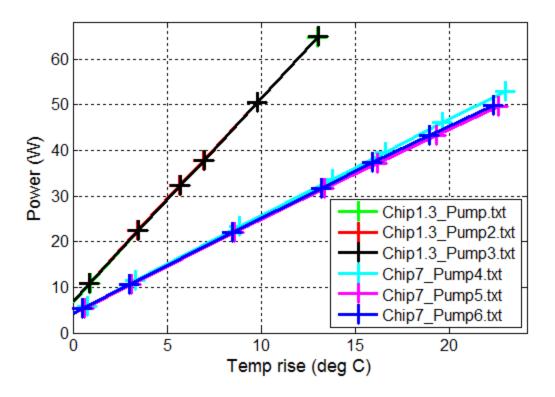

| Figure 23: Plot of resistance vs. power for all the tested chips and each of their tests                                                                                                       |    |

| Figure 24: The dicing cut plan for the module in order to isolate regions of heaters. This picture s the TEA module that is on the backside of the face of the module used during experimentat |    |

| Figure 25: Thermal module with trench cuts for heater isolation                                                                                                                                | 41 |

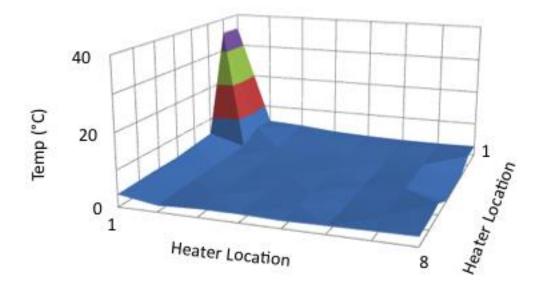

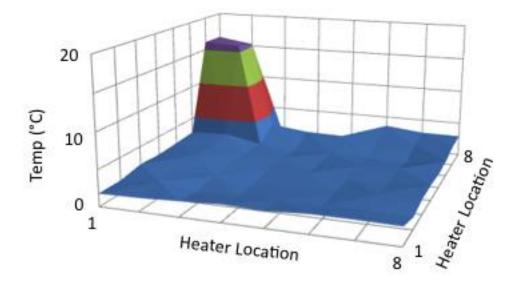

| Figure 26: Module 2 with one heater on with a power level of 1.17 W                                                                                                                            | 42 |

| Figure 27: Module 5 with one isolated heater on with a power level of 1.16 W                                                                                                                   | 42 |

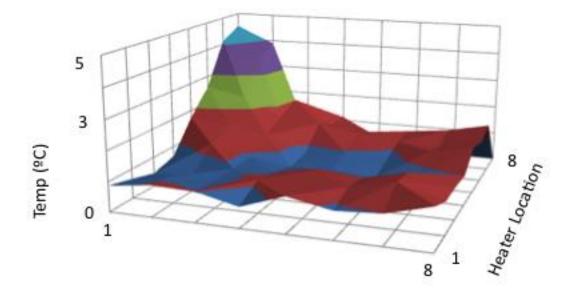

| Figure 28: Module 2 with two adjacent heaters on at a power level of 0.97W                                                                                                                     | 43 |

| Figure 29: Module 5 with two isolated adjacent heaters on at a power level of 0.81 W                                                                                                           | 43 |

| Figure 30: The thermal resistance vs. power of the stacked module (7) and the single wafer silico module (1)                                                                                   |    |

| Figure 31: Power vs. temperature rise of the single wafer silicon module (1) and the stacked silico module (7)                                                                                 |    |

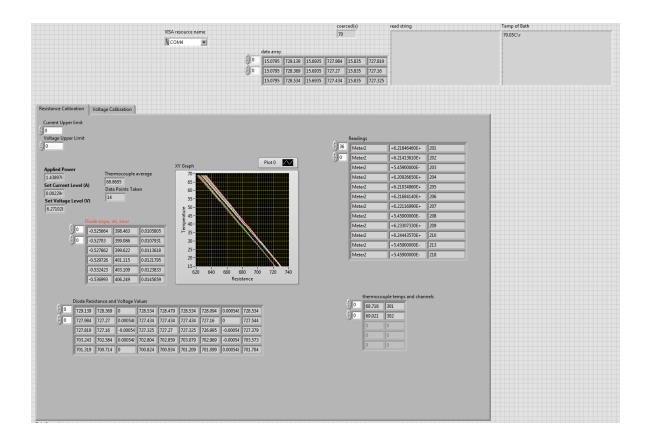

| Figure 32: Diode Calibration Labview <sup>®</sup> Program Operation Panel                                                                                                                      | 57 |

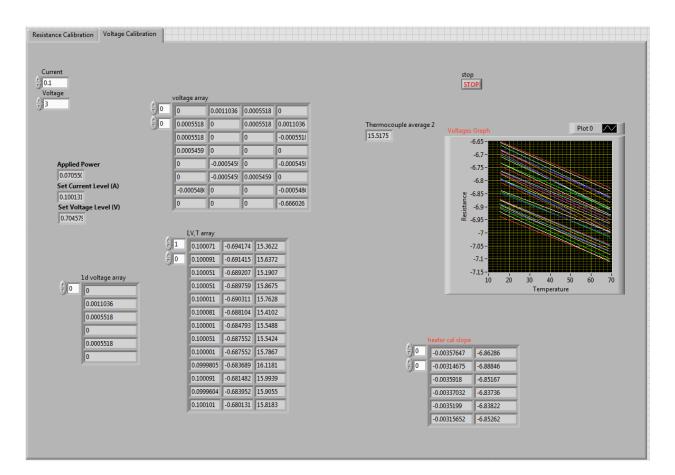

| Figure 33: Heater Calibration Labview <sup>®</sup> Program Operational Panel                                                                                                                   | 58 |

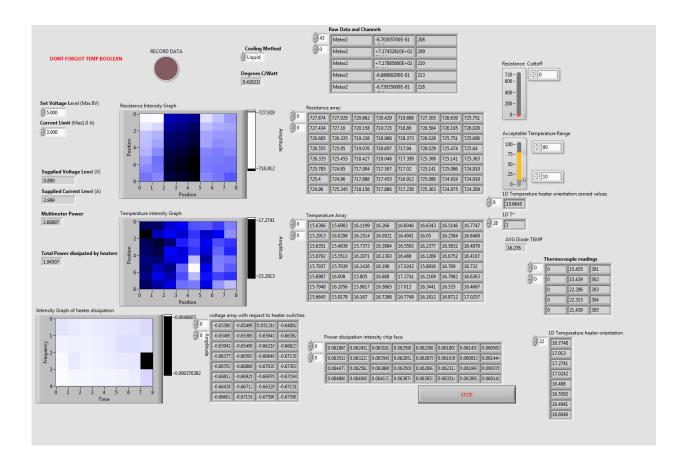

| Figure 34: Operation Panel of Labview Data Interpretation Program                                                                                                                              | 60 |

| Figure 35: Thermal path for the stack of modules                                                                                                                                               | 61 |

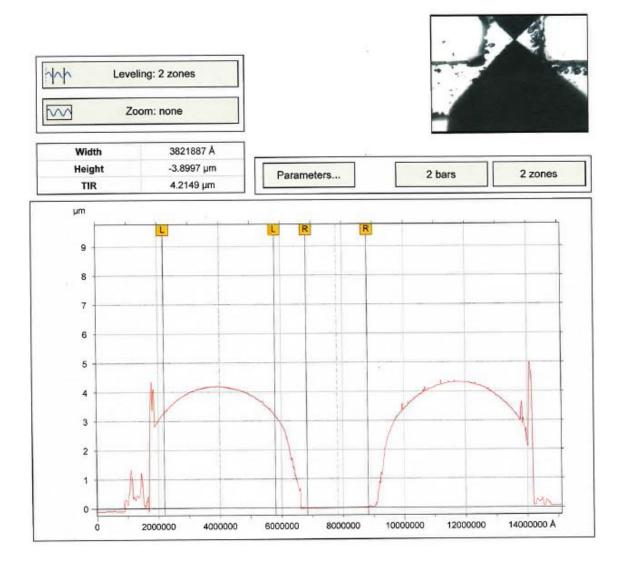

| Figure 36: A Profilometer Data sheet                                                                                                                                                           | 63 |

| Figure 37: Process overview of fabrication of stack                                                                                                                                            | 64 |

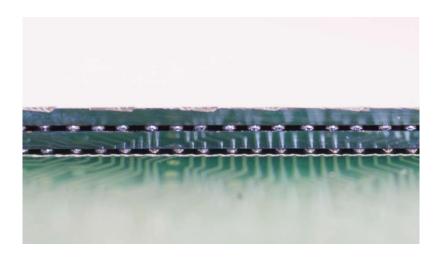

| Figure 38: Sideview of stacked wafer after fabrication                                                                                                                                         | 64 |

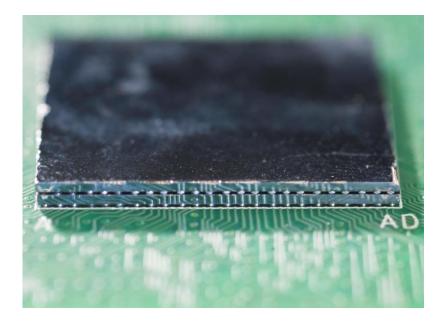

| Figure 39: Stacked wafer after fabrication                                                                                                                                                     | 65 |

|                                                                                                                                                                                                |    |

#### Table of Tables

| Table 1: Composition of the six different wafer types                                                      | 25 |

|------------------------------------------------------------------------------------------------------------|----|

| Table 2: Analysis of all the calibration data                                                              | 37 |

| Table 3: Compilation of thermal test data for each of the four test cases                                  | 39 |

| Table 4: The thermal data obtained from the 2 silicon wafer stack and its single wafer silicon comparison. | 47 |

| Table 5: Average pad height on wafer surface after sputtering operation                                    | 62 |

| Table 6: Summary of module 1 thermal testing data                                                          | 68 |

| Table 7: Summary of module 2 thermal testing data                                                          | 69 |

| Table 8: Summary of module 3 thermal testing data                                                          | 70 |

| Table 9: Summary of module 4 thermal testing data                                                          | 71 |

| Table 10: Summary of module 6 thermal testing data                                                         | 72 |

# **Chapter 1: Introduction**

## 1.1 Problems to be Addressed/Significance

As technological advances continuously miniaturize processor chips, a prominent problem inhibiting the integration of these chips is the thermal load. The chips become too small for the standard heat sinks to effectively dissipate the heat they produce. Therefore, the chip power is limited by the effectiveness of which heat can dissipate rather than its specifications.

One of Draper Laboratory's Internal Research and Development projects is to quantify the effect their integrated Ultra-High Density material (iUHD), an extreme miniaturization packaging method, has on thermal issues. Many entities in the defense, biotechnology and telecommunications markets have a vested interest in this research as thermal issues impede their developing technologies. Figure 1 shows the difference between the typical high power chip and Draper's iUHD embodiment.

#### (a) This is a typical high power chip

#### (b) This is a candidate in Draper's iUHD embodiment

Figure 1: Diagram of difference between typical a high power chip and Draper's embodiment [1]

This thesis provides a thermal characterization of the iUHD material in multi-chip silicon modules. The comparison between modules with bare silicon and varying layers of insulating material and metal traces, which constitute electrical connections between the chips and outside of the module, will help determine the most effective way to promote the cooling of the chip. Potential ramifications of this research include the direct applicability to modules being developed by Draper allowing for their more efficient design through thermal model prediction. Another key inquiry is how the stacking of these modules intensifies these issues. This research is unique in exploring the thermal impact of the novel approach embedding multiple silicon chips (processors, memory) in a silicon carrier wafer and electrically integrating with semiconductor-based dielectric and metal patterning.

#### **1.2 Relevant literature**

A wide variety of research has been conducted in the field of heat transfer through high-density modules. The traditional approach employs a variety of methods ranging from air to liquid coolers with higher efficiencies observed in the liquid coolers [2]. The contact between a liquid cooler and the device can also be improved with thermal adhesive. Thermal adhesive improves the conductance between the cooler and module surfaces promoting heat transfer. However, researchers have also investigated a more efficient means of conducting heat away from the chip using various materials and geometries. One recently researched method of managing the thermal burden in high-density electronics is the use of carbon nanotubes, a material that has a thermal conductivity on the order of 3000 W/Km [3]. Other systems have sought to replace expensive high thermal conductivity materials with cheaper options such as thermal spreaders made from heat pipes [4]. The thermal challenge has become a predominate problem resulting from the shrinking of electronics.

The thermal management of three-dimensional stacks of silicon chips has also been extensively investigated. Zanini et. al. developed a controller for the thermal management of such stacks using active control of on-chip switching rates and active interlayer cooling with pressurized fluids. Their research showed energy savings up to 50% of the state-of-the-art liquid cooling techniques [5,6]. Figure 2 depicts the interlayer cooling technology.

Other efforts to manage the thermal load on multichip devices have revolved around the use of other materials such as SiC instead of Si. SiC has a high range of temperature of operation, approximately 5x higher than that of Si [7].

Packaging technologies are another forefront in which thermal issues are being challenged. Research on package improvement has been taking place over more than two decades. As can be seen in Figure 3, miniaturization of chips has resulted in drastic changes in the Hughes packaging technology from 1970-1990 alone. As is shown, the number of gates per module has increased by a factor of 20 allowing the package to be much smaller than previous packages. This miniaturization of components increases the thermal load by reducing surface area for the heat to dissipate and be managed through heat sinks.

Companies such as Lockheed Martin have been working on improving packaging techniques for years. One of their older technologies was the development of Lockheed Martin High Density Interconnect (HDI) Technology, which used a multi-layer routing to eliminate traditional substrates from multi-chip modules [9]. More recent efforts to improve the power levels and functionality of these chips as they continue to shrink include the development of Draper Laboratory's novel Integrated Ultra-High Density (iUHD) multi-chip integration technology. The main motivation of this thesis is determining the thermal effect of the spin-on dielectric material inherent (SOD) to iUHD in conjunction with metal that forms the electrical traces. The thesis is organized in the following sections. First, a chapter will be devoted to the design of the thermal test system used to investigate the thermal effect of the SOD and the electrical traces. Following this, a chapter will present the experimental results. The thesis will end with a concluding chapter presenting main findings and recommendations for future work. The Appendix includes the supplementary sections covering heater and diode calibration, Labview data interpretation program design, the fabrication of the module stack, the error analysis and more thermal test data.

# **Chapter 2: Design**

This chapter details the design of the thermal test system, which was developed at Draper. The module was designed to emulate the iUHD modules from a thermal perspective. Several key design features include controllable heat dissipation, high spatial density on-chip temperature sensing, a cooling scheme that allows the isolation of the effect of the interconnect layers, and a modular data acquisition (DAQ) that allows easy testing of many different configurations. An "interconnect" layer is defined as a layer of commercial spin-on-dialectric (SOD) insulator plus photopatterned copper traces, roughly 7 µm and 1 µm thick, respectively. One layer is electrically connected to another by drilling vias in the SOD and plating the next layer of interconnect into the holes of the underlying SOD. The following chapter includes sections on the mathematical theory of the thermal resistance network, module fabrication, electrical design, and the design of the module test stand.

#### 2.1 Mathematical Theory of the Thermal Resistance Network

This section discusses the mathematical theory used to determine the thermal resistance of the interconnect layers. First a cross section of the module is shown so the components of the heat path can be observed. This is then generalized into a thermal resistance network, which is then analytically solved.

The high-density chip module is designed to measure the thermal resistance of varying interconnect layers between a heat source and a heat sink as shown in Figure 4. This is done by first calculating the total thermal resistance contribution of the bare silicon module. All the constituents of this module are present in the other chip designs. Therefore, the total thermal resistance of this module includes the thermal resistance of the thermal interface material (TIM), the cooler and the silicon. Once this value is determined, the contribution of the SOD layers can be determined using the assumption of constant thermal resistance contribution of the TIM, cooler and silicon between the modules. Thus the thermal contribution of the SOD layers in a 4-layer module without metal traces is its total thermal resistance minus the thermal resistance of the bare silicon module case. In theory, the only thermal difference between these two modules is the presence of the SOD layers. Therefore the last unknown is the thermal resistance of the SOD, as can be seen in the generic thermal resistance model shown in Figure 5. Potential error resulting from this assumption is discussed in Appendix A.4. The TIM is Omega Therm 201 thermally conductive paste. The uniform application of the TIM was a challenge due to its viscosity and the lack of uniform pressure across the cooler applied directly to it. A laser profilometer was used to determine the thickness of the TIM. After many individual measurements, it was determined the average thickness of the TIM was 7.08-10<sup>-5</sup> m with a 30% variability. Appendix A.4 analyzes the effect of this variability.

Figure 4: Thermal module cross-section [1]

#### Figure 5: Thermal resistance path for testing module [10]

Another crucial assumption for the mathematical model is the ambient temperature is that of the cooler. Therefore the heat sink temperature is known while the calibrated diodes signify the temperature of the source. Similarly, it is assumed that the heat flow is 1-dimensional. This assumption thus states that heat travels solely from the source to the sink through the material layers.

The following is the mathematical theory for determining the thermal resistance of the contributing layers taking into account the previously stated assumptions. After, the method of lumping together the resistances determined constant between modules and treating them as a bulk resistance will be discussed as this was the method employed during testing.

The governing equation for determining thermal resistance is (1) since the thermal path can be simplified to the path shown in Figure 5.

$$R_{wt} = \sum_{i} R_{i} \text{ with}$$

$$R_{i} = \frac{t}{kA} \text{ for conduction through a 1D layer} \qquad (1)$$

$$R_{i} = \frac{1}{kA} \text{ for convective resistance at a surface}$$

Where  $R_{tot}$  is the total resistance,  $R_i$  is the conduction resistance of the *i*<sup>th</sup> component, *t* is the component thickness for a layer component, *k* is the coefficient of thermal resistance for a layer component, *h* is the convective resistance at a surface of the cooler, and *A* is the module surface area.

First, the contribution of the components on the bare silicon chip must be determined. The total thermal resistance of the heat path in a bare silicon module is shown in equation (2). Since the heat flow through bare silicon has been heavily studied, *k* is known and the thickness was determined from the wafer data sheet. The thermal interface material likewise has well documented thermal properties, so the thermal resistance of the grease is known. In order to determine the thickness of the TIM, a Metralight TLE1 Triangulation Laser Sensor was integrated into the test stand for the measurement of this property. Therefore, the thickness of the TIM is a known value with the uncertainty addressed earlier. Lastly, the test data from the bare silicon chip determines the total thermal resistance of the chip or R<sub>tot</sub>. Since we already know the area of the module face, every term in equation (2) is known except *h*, the thermal resistance of the cooler, which is treated as a surface component. It is important to note that the bare silicon module has no interconnect layers so it has no interconnect resistance. Contact resistance is assumed negligible and, furthermore, equal in bare silicon and interconnect cases, so it can be integrated into the cooler resistance estimate.

$$R_{tot} \times A = \left(\frac{t}{k}\right)_{Si} + \left(\frac{t}{k}\right)_{TIM} + \left(\frac{1}{h}\right)_{cooler}$$

(2)

So solving for the unknown *h* results in equation (3).

$$\left(\frac{1}{h}\right)_{cooler} = R_{tot} \times A - \left(\frac{t}{k}\right)_{Si} - \left(\frac{t}{k}\right)_{TIM}$$

(3)

Once this value is determined, an assumption is made that the thermal resistance contribution of the cooler will be equivalent across all tests and chips. This assumption means *h* is now a known value and can be used in the determination of the thermal contribution of the interconnect. It is important to recognize that *h* is a complex function that is usually empirically determined. It depends on many factors including the difference in module vs. ambient temperature. However, the assumption that *h* is approximately the same in different cases was made due to the flow rate and temperature of the cooler being constant for all the tests. For the determination of the thermal resistance of the interconnect, R<sub>INTER</sub>, equation (4) is used. This equation is also based off of Figure 5, however this time there is interconnect layers and therefore an associated resistance.

$$R_{INTER} = R_{tot} \times A - \left(\frac{t}{k}\right)_{Si} - \left(\frac{t}{k}\right)_{TIM} - \left(\frac{1}{h}\right)_{cooler} \quad \text{with}$$

$$R_{INTER} = \left(\frac{t}{k}\right)_{INTER} \tag{4}$$

Since the thickness of the interconnect is known from the processing steps, there is one unknown,  $k_{INTER}$  to solve for. This process can be repeated for all the modules.

However a simpler method was used since the thermal resistance value sought was that of the interconnect. Therefore, as discussed earlier, the total resistance of the bare silicon module was subtracted from the other testing cases to see the contribution of the interconnect layers. Figure 6 visually shows the method. In reality, some of the resistances that are assumed to be fixed actually vary. For example, the variation in the thickness of the TIM makes the resistance of the TIM variable between applications. Figure 7 better exemplifies the resistive contributions of the module components. The error analysis in appendix section A.4 discusses the resulting error from this assumption.

Figure 6: Theoretical contribution of interconnect layers [10]

#### 2.2 Module Fabrication

This section describes how the previously discussed modules for the thermal testing are created. First the commercial-off-the-shelf (COTS) heater components, fabricated by Thermal Engineering Associates Inc. (TEA), that are built on the wafer are discussed in detail. Then the fabrication process for the development of the module layers over the processed wafer is discussed. Lastly the different types of modules created for testing and how they are identified is discussed.

One of the novel aspects of the system is that an embedded multichip module can be emulated using a single silicon chip due to this high spatial resolution of the heater control and temperature sense. This multichip solution uses commercially available heaters from TEA so that the heat flow through the layers of the module can be analyzed. The utilized TEA heater chips have a part number of TTC-1002. A die map of a single die is shown below in Figure 8. Note that two of these individual die make up the "unit cell" referred to in other sections so that an array of 8x8 dies or 4x8 unit cells constitute a module.

The assembled module consists of several key components: the interposer, the populated silicon wafer, and the interconnect as shown in Figure 9. The interposer is a printed circuit board which functions as the path through which all electrical signals must go through to and from the chip. The TEA heater chip provides the capability to selectively heat parts of the chip for thermal analysis on spreading and isolation. On the heater chip is a thermally sensitive diode, which is probed for voltage to determine temperature change. Lastly there is a silicon layer with or without interconnect. The interconnect consists of SOD and metal layers.

Figure 8: Top View of chip produced by TEA Inc.

Figure 9: Embodiment of thermal testing stack up [1]

Five different chip types were fabricated as later detailed in Table 1. One module simply had the TEA die with "front side" interconnect to interface the chip to the interpose and no iUHD interconnect in the thermal path. This was used to determine the contribution of the silicon, thermal interface material (TIM), and cooler to the thermal resistivity of the system. This has been previously referred to as the bare silicon case. As shown previously, this calculation was important in order to determine the effect of metal and high-density layers on thermal resistivity. Therefore, the silicon wafer was patterned with different layers to provide the five types of chips that were to be investigated as shown in Figure 10.

#### Figure 10: Schematic of the backside of the wafer post-processing created by John Burns IV [11].

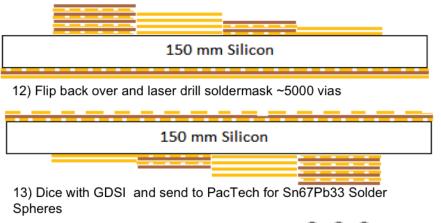

A high level overview of the process to make the wafers is shown in Figure 11. Note that the intervia referred to in the figure is a commercial spin-on-dialectric (SOD). The silicon wafer is bought from TEA with the heater and diodes already populated on the wafer. The wafer is then processed to obtain the final chip to be tested. First the wafer gets a coat of SOD on the active side of the wafer. Then the SOD is patterned using photolithography. A laser is used to drill around 15,000 vias through the chip. A Ti/Cu/Ti layer is then deposited, patterned and etched followed by another coat of SOD. The SOD is engineered to coat with uniform thickness and not fill in holes. The SOD is then patterned again followed by a hardbake and crosslink process. After these steps are completed, the wafer is flipped over

to process the backside. The backside is coated with SOD then patterned once again. Then the layers are built up on this side creating the five different cases using contact masks. These cases are discussed at the end of the section. Lastly the wafer is flipped back over and the soldermask is laser drilled. The soldermask is a patterned layer of the SOD. The completed wafer is then diced to form and 8x8 array of active die, thus forming the chip size compatible with the thermal testing stand. The wafer has 100  $\mu$ m streets designed for the dicing operation. Since the wafer was patterned with gold pads that form a ball grid array, adhesion to the interposer board is facilitated after the chip is bumped.

1) Active die facing upwards

150 mm Silicon

2) Coat with Intervia

150 mm Silicon

3) Pattern Intervia with Mask Name: DRAPER LABORATORY Thermal Die Front Dice r1 121206 (dicing streets)

#### 150 mm Silicon

4) Laser Drill Vias (Exported from L-edit) ~15000 vias

150 mm Silicon

5) Ti/Cu/Ti layer, deposit, pattern, etch. Pattern with Mask Name: DRAPER LABORATORY Thermal Die Front Met r1 121206

150 mm Silicon

6) Coat with Intervia

150 mm Silicon

7) Pattern Intervia with Mask Name: **DRAPER LABORATORY Thermal Die Front Dice r1 121206**, hardbake, crosslink. Note: use conformal sheet on EVG so the vacuum holds.

150 mm Silicon

8) Flip over and process backside of the wafer (No handle attach)

9) Coat with Intervia

10) Pattern Intervia with Mask Name: DRAPER LABORATORY Thermal Die Back V12 r1 121206

11) Build up multiple layers with the 5 different cases using contact masks

Figure 11: High-level process flow for chip fabrication created by John Burns IV. [11]

After processing, the silicon wafer is diced and bumped with solder balls so that the wafer

components can be mounted on the PCB. After alignment between the PCB and the processed wafer,

the components are reflowed in an oven resulting in the assembled chip module.

Table 1 describes the composition of the 6 different types of modules used during testing. The differences in the modules are the number of SOD layers, presence of metal traces and whether the module consists of a stack of wafers.

| Module  | Number of<br>SOD layers | Metal (Y/N) | Number of<br>stacked<br>wafer pieces |

|---------|-------------------------|-------------|--------------------------------------|

| 1 and 6 | 0                       | N           | 0                                    |

| 2       | 2                       | N           | 0                                    |

| 3       | 4                       | N           | 0                                    |

| 4       | 4                       | Y           | 0                                    |

| 5       | 2                       | Y           | 0                                    |

| 7       | 0                       | N           | 1                                    |

Table 1: Composition of the six different wafer types

#### **2.3 Electrical Design**

This section discusses the electrical design of the fabricated module. One module contains 64 diodes in an 8x8 array and 32 heaters in a 4x8 array diced from the fabricated wafer in section 2.2. This section includes the operational theory of the device, which involves the use of heaters and diodes to stimulate and read the thermal state respectively. The diodes are linearly sensitive to temperature with a constant current supply, which can be observed in the voltage change.

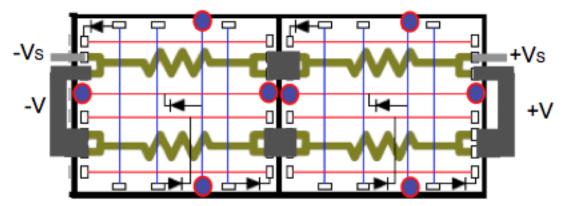

64 diodes are used for measuring temperature through voltage change. As the chip heats up, the voltage drop across the diodes for a constant current linearly reduces allowing the temperature change to be determined after calibration. Diodes where chosen as the means for measuring temperature due to the ease of monolithic fabrication along with high sensitivity not seen in other temperature sensors such as thermocouples. The implementation of diodes for temperature measurement is a standard practice and is compatible with standard chip processes. Data is received by DAQ devices and monitored through a Labview program, as detailed in section 2.4. There are 32 controllable heaters groups on each chip. The heater diodes are monolithically fabricated on top of each other in the TEA silicon die using standard semiconductor foundry processes. This allows specific regions of the module to be selectively heated. The diodes and heaters are mapped onto the chip face as shown in Figure 12. This figure shows the adjacent heaters wired together and the access points for the 4-point probe of the thermally sensitive diodes. The white rectangles with a black outline are pads, the circles with red outlines are probing points and the arrows are the diodes. The diodes used are in the center of each square unit. The probing points are for the four point probing method where current is driven from one pad through the diode and to another pad and the voltage drop is read through the other two pads. The diodes at the top left of each unit and at the bottom of each unit are not used because there is no need for that much information especially since it complicates the interface to the DAQ.

Figure 12: Two diodes with the heaters wired together such that one switch turns on the heater for both chips [1]

Each unit cell of the heater/sensor array contains 2 heaters and 4 probe areas for temperature sensing. Adjacent heaters are connected together resulting in an array of 4x8 heaters and an 8x8 array of thermally sensitive diodes. Through the observation of the voltage drop across the individual diodes

for a constant current, temperature change can be determined. An analysis of the accuracy of this method is discussed in Appendix section A.4.

The voltage drop of the thermally sensitive diode is determined by using the 4-point probe method to supply constant current on two of the wires and measure voltage locally across the diode with the other two. This method increases accuracy of the readings since it effectively eliminates the resistive contribution of sources other than the thermally sensitive diode.

The design and the wiring of the heaters serve a multitude of purposes. For one, the wiring allows the individual control of the heaters, which results in a higher density of information from the chip. Through the individual heater sites, the overall power consumption of the device can be accurately determined and the amount of power that is being generated by a heater local to each pair of diodes can be observed. The accuracy of the power measurements involving the heaters is discussed in Appendix section A.4.The diodes consume negligible power since they draw approximately 0.7 mW. Since each diode is read individually and not simultaneously, 0.7 mW is the total loss of power through the diodes. The power being driven through the chip is over 4 magnitudes higher than this value. There are no more losses from the setup due to the utilization of the 4-point probe method. This eliminates the resistances of the thermal test stand components from the data obtained from the module. However, to improve accuracy, quantifying the resistance of the thermal test stand can be done in future work. The power supplied to the thermal test stand was greater than the power received by the chip heaters for this reason. The potential areas for power loss in the system include the thermal test stand PCB connections, the solder balls, the interposer, and the wires to the DAQ. Anecdotally, the bulk of the resistance appears to be on the thermal test stand board as some electrical lines were fried under high power levels. The investigation into these resistances may indicate whether the cooler is pulling out more heat from the module than is given off by the heaters. A mass flow analysis can be done to see if the heater is indeed taking away extra heat. Therefore this future work would increase the accuracy and sensitivity of the device.

The TEA chip was designed so that heater resistances optimized current and voltage requirements. If the heater resistance were too low, a high current would be needed to obtain a given power level which would make power delivery instrumentation more difficult and potentially adversely affect the system through electromigration. If the resistance were too high, the voltage required for a given power level would be prohibitive to the power supply. The resistive heating produced by driving a fixed resistor with a DC voltage or current source is described by Ohm's Law and the electric power equation

$$P = \frac{V^2}{R} \tag{5}$$

And

$$P = I^2 R \tag{6}$$

where *P* is power in watts, *V* is the voltage in volts, *I* is the current in amps and R is the resistance in ohms. Therefore the  $V^2$  and  $I^2$  terms must compensate for all changes in *R* in order for *P* to remain constant.

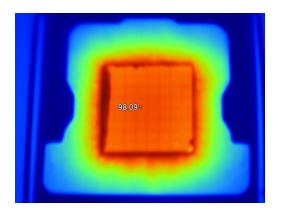

Figure 13 is an IR image of the un-sinked module that shows the 8x8 grid of diodes at nominal operation near 100°C.

Figure 13: Thermal picture of module with all the heaters on with a surface temperature of 98.09°C

### 2.4 Design of Module Testing Stand

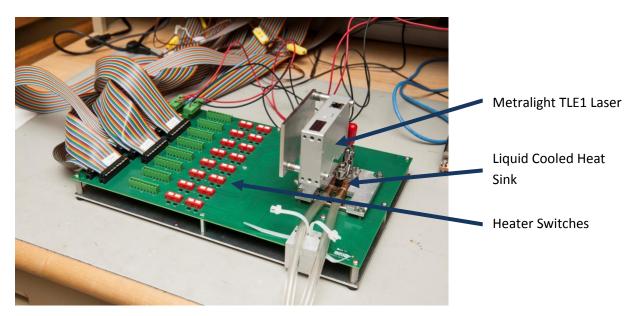

The testing stand was designed in order to facilitate independent heater control and individual diode measurement. These capabilities result in a high density of information coming from the module. 64 different locations are being actively probed for temperature and 32 heaters can be manually controlled to heat regions of the chip. The setup is shown in Figure 14.

Figure 14: Thermal Test Stand

A Metralight TLE1 Laser was used to provide an estimation of the thickness of the thermal interface material (TIM). The tool has an advertised resolution to 1 µm. The way the instrument was used is shown in Figure 15. The thickness of the TIM was needed in order to reduce the variables in the 1-D thermal equation described in section 2.2. The laser was used to first read the surface height of the module without TIM then again once TIM was applied. Due to its design, the height was read in respect to the surface of the laser mount, giving a consistent standard to measure against. This allows the deduction of the thickness of the TIM. The surface topology of the TIM was not uniform; however an average height across the lasers span was used to estimate the true TIM thickness. Since this technology is in its infancy, the program that operates the laser had glitches making it hard to use. Repeatability of the measurements was often a concern as variations were observed in measurements that should be similar. It was therefore decided that the thickness for the TIM would be averaged over many trials and the resulting average thickness would be used for the thermal calculations.

Figure 15: Graphic showing use of Metralight Triangulation Laser [10]

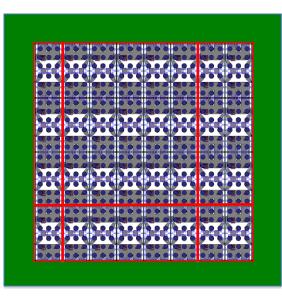

The testing stand also has a bank of red heater switches running down the middle of the board. Each heater corresponds to a region on the chip module. Flipping the switch to the on position causes the associated module region to heat up resulting in heat spread. A mapping of the heater switch to chip surface location is shown in Figure 16. This figure is divided into colored regions to facilitate the ease of reading and representative of the trench locations discussed in section 3.3. This will be utilized later in section A.1 as part of calibration and section 3.3 during the thermal isolation experiment. Note that the heater switches are labeled in Figure 14.

| H1  | H2  | нз  | H4  |

|-----|-----|-----|-----|

| H5  | H6  | H7  | H8  |

| H9  | H10 | H11 | H12 |

| H13 | H14 | H15 | H16 |

| H17 | H18 | H19 | H20 |

| H21 | H22 | H23 | H24 |

| H25 | H26 | H27 | H28 |

| H29 | H30 | H31 | H32 |

| H29 | H25 | H21 | H17 | H13 | Н9  | H5 | H1 |

|-----|-----|-----|-----|-----|-----|----|----|

| Н30 | H26 | H22 | H18 | H14 | H10 | H6 | H2 |

| H31 | H27 | H23 | H19 | H15 | H11 | Н7 | НЗ |

| H32 | H28 | H24 | H20 | H16 | H12 | H8 | Н4 |

Figure 16: The mapping of heater switches to the module surface. The left diagram represents the heater switches and the right diagram represents the corresponding heater locations looking down at the module face.

Rainbow ribbon cable makes the connections between the test stand PCB and the multimeters.

Three three-level multimeters are used to interpret the signals. The multimeters are then hooked up to

a Labview program where the data is read and interpreted. Figure 17 shows the overall design of the

thermal test stand.

The testing stand was designed in order to facilitate the quick exchange of the five different types of chip modules in the structure. The primary method that the modules were made easily interchangeable was the latch down mechanism shown in Figure 18. The mechanism press fits the back of the chip module onto pins on the thermal test board thus completing the electrical circuit.

Figure 17: Overview of testing apparatus

Figure 18: The latching mechanism clamps down around the edges of the module creating an electrical path between the module and the PCB

The copper heat sink, shown in Figure 19, is secured on the top of the chip module by a rubber stopper mounted on a metal frame as shown in Figure 20. The metal frame also functions to align the heat sink over the surface of the module. The stopper is mounted on a screw, so the pressure applied to the heat sink can be adjusted. The fixture was also made so that other types of heat sinks could readily be switched onto the Thermal Test Stand board. Two Intel heat sinks, the recommended 2U heat sink with an integrated heat pipe and a fan and the recommended 1U heat sink without a fan, were used in other experiments comparing the effectiveness of heat sinks. This data will not be shown in this report due to repeatability concerns. However, the thermal test stand was designed to incorporate a variety of heat sinks.

Figure 19: The liquid cooled heat sink used on the thermal test stand

Figure 20: Components of the module attachment to the thermal test stand are shown above. The rubber stopper and the metal frame secure the cooler during testing.

The thermal test stand also has a bank for the power supply to connect to the board. The power supplied was driven by either the voltage set or the current set, depending on the resistance of the system during the test. For example, if one heater was being tested, the current set point would be the actual current but the voltage would only be what the test stand drew. However, if all the heaters are being tested, the voltage set point would be the actual voltage and the current would be driven by the draw of the board.

A Labview program interprets the data obtained by the multimeters. The structure of the Labview program is discussed in Appendix section A.2.

# **Chapter 3: Experimental Results**

### **3.1 Results of Diode and Heater Calibration**

The calibration of the diodes and the heaters on each of the modules was conducted at least twice to ensure consistent results. Each calibration resulted in a slope and intercept for the linear model of the dependence of diode resistance on temperature. Since all the modules have diodes and heaters fabricated by the same process, variation between them should be minimal. However, there are differences that arise and can be seen in the data. Figure 21 and Figure 22 show the diode calibration and the heater calibration respectively. As can be seen, there is a range of calibration curves. Each calibration file for a module contains 32 or 64 slopes and intercepts depending on the calibration type. It should be noted the sensitivity of the heaters to temperature change is significantly smaller than the diodes as they are not designed to vary significantly with temperature change due to their function as a heat source.

Figure 21: Calibration plot for the 64 diodes of one of the modules. Each diode has a specific calibration line. Each module has a similar looking plot.

In order to determine the variation among the diodes and the heaters, all the calibration data was combined and analyzed. Among all the trials, the average slope of the diode calibration line was determined to be  $-0.54^{\circ}$ C/ $\Omega$  while the average slope of the heater calibration line was determined to be  $-0.0038^{\circ}$ C/ $\Omega$ . The standard deviation of both sets of slopes was determined to be  $0.03^{\circ}$ C and  $0.0034^{\circ}$ C respectively. Similarly, the variation in the intercept values was analyzed with the mean and the standard deviation away from that mean. This data along with the previously mentioned data can be found in

| Calibration<br>Component | Average Slope | Standard<br>Deviation | Average<br>Intercept | Standard<br>Deviation | Average<br>Variance from<br>Best Fit (°C) |

|--------------------------|---------------|-----------------------|----------------------|-----------------------|-------------------------------------------|

| Diodes                   | -0.54 °C/Ω    | 0.03 °C               | 465.80 °C            | 24.34 °C              | 0.02                                      |

| Heaters                  | -0.0038 Ω/°C  | 0.0034 Ω              | -6.87 Ω              | 0.68 Ω                | N/A                                       |

Table 2.

| Calibration<br>Component | Average Slope | Standard<br>Deviation | Average<br>Intercept | Standard<br>Deviation | Average<br>Variance from<br>Best Fit (°C) |

|--------------------------|---------------|-----------------------|----------------------|-----------------------|-------------------------------------------|

| Diodes                   | -0.54 °C/Ω    | 0.03 °C               | 465.80 °C            | 24.34 °C              | 0.02                                      |

| Heaters                  | -0.0038 Ω/°C  | 0.0034 Ω              | -6.87 Ω              | 0.68 Ω                | N/A                                       |

### Table 2: Analysis of all the calibration data

### 3.2 Results from Modules with Differing Layers

Appendix A contains the tables summarizing the data obtained from the testing modules.

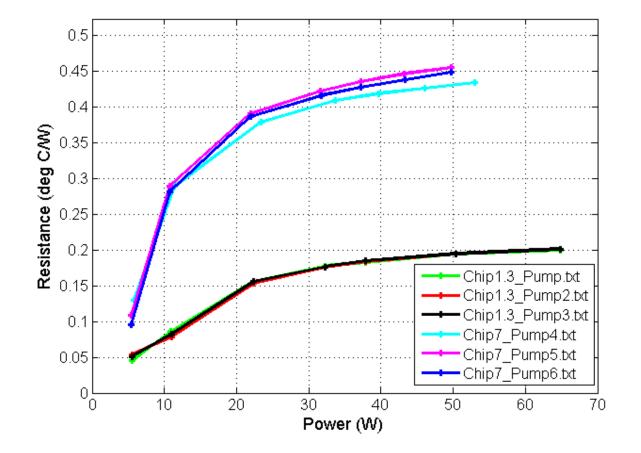

Module 6 and Module 1 are both composed of bare silicon. Since these two were from the same wafer

and batch of chips they were given different identification numbers. Module 5, consisting of 2 layers with metal, was not successfully fabricated with this batch. The thermal spreading analysis however utilizes a module 5 fabricated from another batch. The plot below shows the thermal resistance of each of the modules in three trial runs. Table 3 shows the breakdown of the pertinent data obtained from these chips. The average total resistance was taken from all the data points excluding module 6's 1<sup>st</sup> data points due to the uncharacteristic slope shown. Potential sources of this slope could be the cooler block cooling down the testing fixture rather than just the module. When the module is not giving off much heat, the test fixture may be a significant source of heat. However, as the module starts to give off more heat, the cooling of the thermal test stand becomes minimal in comparison. Another source of the slope could be due to the assumption that the heat transfer coefficient *h* is constant. In reality, *h* changes due to a variety of factors including the change in the delta temperature between the source and the sink. This assumption should be further investigated as more tests are conducted. As can be seen in Figure 23, most of the plotted lines appear to approach a steady state as power increases. Therefore an accurate estimate of the thermal resistance of the modules over the temperature range is provided through the averaging of all the data points in a particular line.

Figure 23: Plot of resistance vs. power for all the tested chips and each of their tests

| Case                                 | Average<br>Total<br>Resistance<br>(°C/W) | Standard<br>deviation of<br>measurement<br>(°C/W) | Resistance<br>delta vs.<br>Silicon-only<br>case (°C/W) | Calculated<br>effective<br>conductivity<br>(W/mK) | Resistance<br>increase per<br>layer of<br>interconnect<br>(°C/W) |

|--------------------------------------|------------------------------------------|---------------------------------------------------|--------------------------------------------------------|---------------------------------------------------|------------------------------------------------------------------|

| (3) Four<br>layers, no<br>metal      | 0.539                                    | 0.017                                             | 0.308                                                  | 0.22                                              | 0.077                                                            |

| (2) Two<br>layers, no<br>metal       | 0.368                                    | 0.015                                             | 0.138                                                  | 0.24                                              | 0.069                                                            |

| (4) Four<br>layers,<br>with<br>metal | 0.363                                    | 0.015                                             | 0.133                                                  | 0.51                                              | 0.033                                                            |

| (1&6)<br>Silicon                     | 0.231                                    | 0.025                                             | N/A                                                    | N/A                                               | N/A                                                              |

#### Table 3: Compilation of thermal test data for each of the four test cases

An important observation of the graphed data is that the thermal resistance of the chips is ranked as follows: Silicon < four layers with metal < two layer no metal < four layers no metal. There are two expected consequences of this. First the silicon only module had the lowest resistance as it had the least material impeding heat flow. As is shown, the addition of layers affects the thermal resistance. Second, the incorporation of metal helps heat flow through the module. From the data shown in Table 3, the metal improves the thermal conductivity by a factor of 2. It appears that the addition of layers of SOD and the contribution of metal can have a 0.133-0.308 °C/W effect on the thermal resistance of the silicon-based module. The determination of this contribution was one of the main goals of this work. It is important to note the consistency between trials of each module. All the tests for a module follow the same trend, helping affirm the validity of the data.

### **3.3 Results of Heater Isolation**

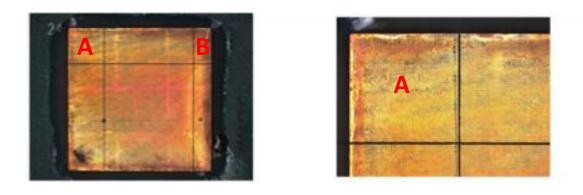

A module was diced with a 70 µm blade in order to isolate heater regions so that a heat-spread study could be conducted. Three dicing cuts were made so that 6 regions of varying sizes were formed. The schematic for the cuts are shown in Figure 24 below. This image is shown as if the metal, silicon and SOD layers covering the TEA module were see-through. The cuts went completely through the module but did not cut through the interposer board so that no electrical connections were disturbed.

Figure 24: The dicing cut plan for the module in order to isolate regions of heaters. This picture shows the TEA module that is on the backside of the face of the module used during experimentation.

The trench cuts on the module surface are shown in Figure 25. The chip chosen for this study consists of

2 layers of SOD with metal.

Through the isolation of heater regions, temperature gradients can be observed over the 70  $\mu$ m gap between the parts of the wafer. This information will help determine the effect heat spread has on the overall thermal resistance of the module.

Care must be taken during the application and removal of the TIM so as not to fill the trenches on the module. This would result in the bridging of the heat path across the surface of the chip. Therefore, after every trial, the module was subjected to an ultrasonic bath in order to remove all remnants of the TIM from the trenches.

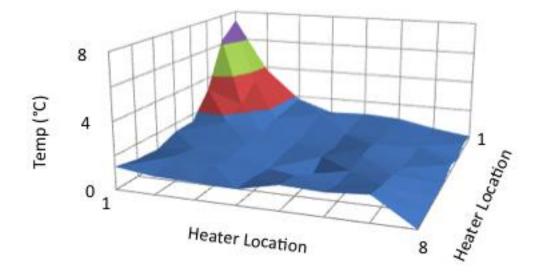

The main analysis conducted was on the heat spread of an isolated region with two heater units and a region with one heater unit. These regions are labeled A and B respectively in Figure 25.

The thermal spreading analysis was done by comparing module 5 with trench cuts, as previously stated, and module 2 without trench cuts. The decision was made to use module 2 as a comparison due to only one successful fabrication of module 5 and due to the fact that they both are composed of silicon and the same number of layers of SOD. The testing was done on two sections of the modules. One section isolated one heater while the other isolated two heaters. The results are shown below.

Figure 26: Module 2 with one heater on with a power level of 1.17 W

Figure 27: Module 5 with one isolated heater on with a power level of 1.16 W

Figure 28: Module 2 with two adjacent heaters on at a power level of 0.97W

Figure 29: Module 5 with two isolated adjacent heaters on at a power level of 0.81 W

As expected, the trench cuts effectively eliminated the heat spread throughout the chip thus greatly reducing the effectiveness of the heat sink. The isolated 1-heater region had temperatures approximately five times higher as compared with the module without the trench cuts. The isolated 2-heater region had temperatures approximately four times higher as compared with its non-isolated counterpart. It is important to note that the power levels for the 1-heater regions were almost identical with a 0.1 W difference and the power level for the 2 heater regions was 0.17 W different. Since the testing system is current dependent with the required voltage drawn, it is challenging to get the exact same power level between tests.

### **3.4 Results of Module Stack**

The thermal analysis of the stack was done by comparing the total thermal resistance of the stack to that of a single bare silicon chip. As discussed in Appendix A.3, the stack was fabricated with two bare silicon chip pieces stacked and adhered together by solder balls. The top chip was not electrically connected and served the purpose of simulating the heat path of a stacked module. The attachment

process mirrors the methods used in actual application very closely so this setup can be an accurate thermal analog to a functional chip stack. Both the single wafer silicon module and the stacked silicon module were tested three times to establish repeatability. The results for the thermal resistance vs. power applied are shown in Figure 30. Potential reasons for the observed slope are discussed in section 4.2. A plot showing the temperature rise of the module vs. power applied is shown in Figure 31.

Figure 30: The thermal resistance vs. power of the stacked module (7) and the single wafer silicon module (1).

Figure 31: Power vs. temperature rise of the single wafer silicon module (1) and the stacked silicon module (7)

Table 4 shows the breakdown of the pertinent data for the two cases. As can be observed, the addition of the second wafer to the thermal path affects the thermal resistance by a magnitude greater than 2. This is likely because the addition of the second wafer layer not only adds thermal resistance by doubling the amount of silicon in the thermal path, but also adds thermal resistance by forcing the heat path through the solder balls which connect the two chips. The SnPb solder balls are high conductivity balls, but have a thickness of roughly 375µm after reflow and cover approximately 27% of the surface area of the chip face. It is this thickness and low surface area that likely contributes to the thermal resistance of the stack.

| Case                     | Average Total<br>Resistance<br>(°C/W) | Standard<br>deviation of<br>measurement<br>(°C/W) | Resistance<br>delta vs.<br>Silicon-only<br>case (°C/W) |

|--------------------------|---------------------------------------|---------------------------------------------------|--------------------------------------------------------|

| 2 silicon<br>wafer stack | 0.422                                 | 0.023                                             | 0.24                                                   |

| Silicon                  | 0.182                                 | 0.016                                             | N/A                                                    |

Table 4: The thermal data obtained from the 2 silicon wafer stack and its single wafer silicon comparison.

# **Chapter 4: Conclusions**

### **4.1 Contributions to Field**

One of the most significant contributions this research provides is isolating the effect of SOD layers in controlled environments. This provides data that can be used for more complicated thermal models which would be more challenging and more expensive to test. This data also directly addresses the concerns of the increased thermal load associated with miniaturization of chips as it quantifies the thermal effect of a high density material. This information can be used to assist in the design of chips to reduce this thermal load.

The results show the impact of adding SOD layers, metal traces, and stacking chips to the thermal resistance. All of these operations are currently being used without quantification of their impact. Also the effect of reducing heat spreading was examined through heater isolation. This simulated the challenges in sinking heat from a source as the surface area is decreased. Although there are sources of error in the measurements, there is confidence in the measurements as discussed in Appendix section A.4.

### 4.2 Future work

First the assumption of the thermal coefficient being constant throughout the test must be investigated. As can be seen in the results, the thermal resistance appears to initially have a steep slope over low powers. This may be because the delta temperature between the source and the sink is low at these points changing the thermal coefficient. In a similar vein, analysis should be conducted to see if the cooler is taking away extra heat from the module. There is a big disparity between the power supplied by the power source and the power supplied to the heaters, meaning a heat source could be present in another part of the module. Investigating this by analyzing the resistance of the thermal test stand components and the mass flow of the cooler would increase the accuracy and sensitivity of the results.

An important next step in the determination of the thermal resistance of the high-density processor packaging method is determining variability on a larger scale. This involves testing modules from different wafers to insure the fabrication process doesn't have any inherent variability. Preliminary tests with the second batch of modules indicate very low variability. However, to insure this, more than two wafers need to be fabricated. Due to time and cost constraints, this hasn't been previously investigated.

More modules will also allow the variability of the thermal spreading analysis to be quantified. Due to lack of materials and time, more diced wafers could not be produced. Also a direct comparison between the same types of module (trench cut vs. not) would increase the accuracy of the results on the effect of the trenches on heat spreading. This will involve dicing more trenches into the different types of modules to see if have a varying effect. Another way the thermal spreading analysis can be improved is by implementing a method to get identical power levels into the modules so that their thermal response can be compared more accurately.

As more modules are being produced, the tests for the stacking of the wafers can be furthered. This involves doing more tests on different combinations of stacked wafers. One stack planned is a 2wafer stack of silicon wafers with SOD layers. This will then be able to be directly compared to the bare silicon 2-wafer stack and the thermal effect to the SOD on a larger scale can be analyzed. Another area to be investigated is increasing the stack height. There has been interest at Draper to make a stack as tall as three wafer pieces. The method for fabricating this stack would be identical to the fabrication of the 2-wafer stack, a method that has proved successful. Lastly, one important implication of this research is how it affects current Draper projects. As such, the module can be redesigned to directly mimic Draper modules in order to determine their thermal characteristics and establish methods for thermal management. This is a primary motivation for the research, and this future work would increase the fidelity and applicability of the results.

# References

- [1] Smith, Brian. "Charmin, iUHD Thermal Test Capability for TP." Design Review. 4 October 2012. Draper Laboratory internal document

- [2] Kandlikar, Satish G. and Hayner II, Cliford N. (2009) "Liquid Cooled Cold Plates for Industrial High-Power Electronic Devices—Thermal Design and Manufacturing Considerations," Heat Transfer Engineering, 30: 12, 918-930.

- [3] Lingbo Zhu; Hess, D.W.; Wong, C.P., "Assembling Carbon Nanotube Films as Thermal Interface Materials," *Electronic Components and Technology Conference, 2007. ECTC '07. Proceedings.* 57th , vol., no., pp.2006,2010, May 29 2007-June 1 2007

- [4] Avenas, Y.; Ivanova, M.; Popova, N.; Schaeffer, C.; Schanen, J.-L.; Bricard, A., "Thermal analysis of thermal spreaders used in power electronics cooling," *Industry Applications Conference, 2002. 37th IAS Annual Meeting. Conference Record of the*, vol.1, no., pp.216,221 vol.1, 13-18 Oct. 2002

- [5] Brunschwiler, T.; Paredes, S.; Drechsler, U.; Michel, B.; Wunderle, B.; Reichl, H., "Angle-of-attack investigation of pin-fin arrays in nonuniform heat-removal cavities for interlayer cooled chip stacks," *Semiconductor Thermal Measurement and Management Symposium (SEMI-THERM),* 2011 27th Annual IEEE, vol., no., pp.116,124, 20-24 March 2011

- [6] Brunschwiler, T.; Paredes, S.; Drechsler, U.; Michel, B.; Cesar, W.; Toral, G.; Temiz, Y.; Leblebici, Y.,

"Validation of the porous-medium approach to model interlayer-cooled 3D-chip stacks," *3D System Integration, 2009. 3DIC 2009. IEEE International Conference on*, vol., no., pp.1,10, 28-30

Sept. 2009

- [7] Hornberger, J.M.; Cilio, E.; Schupbach, R.M.; Lostetter, A.B.; Mantooth, H.A., "A High-Temperature Multichip Power Module (MCPM) Inverter utilizing Silicon Carbide (SiC) and Silicon on Insulator

(SOI) Electronics," *Power Electronics Specialists Conference, 2006. PESC '06. 37th IEEE*, vol., no., pp.1,7, 18-22 June 2006

- [8] Licari, J.J., "Fabrication and packaging of high-density multichip interconnect (HDMI) substrates," Aerospace and Electronics Conference, 1989. NAECON 1989., Proceedings of the IEEE 1989 National, vol., no., pp.1682,1688 vol.4, 22-26 May 1989

- [9] Dufour, B.; McNulty, M.; Miller, S., "Microwave multi-chip module utilizing aluminum silicon carbide with in-situ cast components and high density interconnect technology,"*Multichip Modules,* 1997., International Conference on , vol., no., pp.309,314, 2-4 Apr 1997

- [10] Smith Brian. "Thermal Stand Test Philosophy." Internal document. 19 June 2013.

- [11] Burns, John IV. "FT-Live Dicing Request." Internal document.

# Appendix

### A.1 Individual Diode and Heater Calibration

In order to obtain accurate information from the module, both the diodes and the heaters were calibrated. This was done through the implementation of a Labview® program with a process for diode calibration and another for heater calibration. The diode calibration is run first as the heater calibration is dependent upon its resulting data. The diodes were individually calibrated in order to minimize error resulting from the variation of resistance and thermal sensitivity of the diodes. Therefore the diode calibration resulted in 64 equations for the conversion of resistance to temperature. As stated previously, this calibration was based on the assumption that the ambient temperature is that of the liquid cooled heat sink. Two thermocouples, one at the inlet and one at the outlet of the cooling block, were averaged in order to determine this temperature. The thermocouples used were Cole-Palmer 2.5" Type K thermocouple probes. Since the probe tips were designed for penetration, one probe went into the tubing directly before entering and one right directly after exiting the liquid cooled heat sink. The probes were placed to be as close to the liquid cooled heat sink as possible. The temperature of the heat sink is controlled by a Cole-Palmer Polystat bath and circulator. Since the resistances of the diodes are designed to vary linearly with temperature, the calibration equation is of the following form:

$$T = m \times r + b \tag{7}$$

Where T is the temperature of the diode, m is the slope constant determined from calibration, r is the resistance read at the diode, and b is the vertical offset at the Y-axis determined from calibration.

Calibration data was also analyzed for the r<sup>2</sup> value of the linear fit, which proved the efficacy of the linear model.

The resistance of the diodes was taken three times at five temperatures: 16°C, 30°C, 40°C, 55°C and 70°C. This resulted in plot of 15 points for every diode. Each set of data was then used to determine the diode's best-fit line.

The calibration of the heaters was done to account for the thermal variation of the heating element. Since these resistors were not designed to be thermally sensitive, the test was done at only two temperatures: 16°C and 70°C. Therefore the heater resistance change observed in respect to temperature changed will be much less significant than with the diodes. However, this calibration is important in order to determine the amount of power going to each heater so that the actual power being dissipated by each region and in the entire module can be analyzed.

The heater calibration process is done through the application of a specific current and drawn voltage to each individual heater at each of the temperature levels. Since the resistance of the heater resistors cannot be directly determined, the following analysis was done.

$$R_H = \frac{V_H}{I_H}$$

(8)

Where  $R_H$  is the resistance,  $V_H$  is the voltage drawn and  $I_H$  is the current applied to the heating element. This allows the use of a linear fit to model the equation thus resulting in the following.

$$R_H(T_H) = m_H \times T_H + b_H \tag{9}$$

Where  $T_H$  is the temperature of the heating element,  $m_H$  is the slope of the fit and  $b_H$  is the y-intercept of the best fit line.

Since the switch to turn on the heaters is physical, the process is a little tedious as it involves the flipping of 64 switches. A waiting period allows the module to reach steady state before data is taken. Therefore each heater will have two data points, one at each temperature. The linear fit of the heater resistance change with temperature shows a very small slope, however this data is still used in the Labview program designed for power tests of the modules since it helps to reduce error. The temperature of the heater resistors were determined by averaging the temperature determined from the two diodes each heater directly impacted.

Both the diode and heater calibration were run multiple times in order to ensure repeatability of the results.

### A.2 Labview Data-Interpretation Program Design

Labview controlled the thermal testing stand in order to automate as much of the process as possible. Depending on whether the module was being calibrated or tested, different Labview programs were developed and used.

The diode calibration program was designed to determine diode temperature as outlined in section A.1. The user interface for the diode resistance of the calibration VI is shown in Figure 32. As can be seen, the resistance of the diodes are read out in raw format and shown on the screen under "Readings." This array gives the meter, resistance and the location in the meter. The "thermocouple average" data field shows what the estimated surface temperature of the chip is for calculation. Directly below, the "data points taken" box counts the total number of data points recorded so it can be determined where in the process the program is in data collection. As the data points are taken, the "Diode slope, int, error" fields are populated with the slope, intercept and error of the best fit line though the data. This data is then graphically represented in the XY plot so that the any outlier behavior among the diodes can be identified. The "diode resistance and voltage values" array outputs all the raw data being read by the multimeters in a row with each subsequent reading populating the next row. The slope and intercept data along with the raw data are then saved to separate .txt files.

The program also uses serial communication with a cooler to set the surface temperature of the chip. Since the program is automated, steady state is ensured through the implementation of a three-minute wait time.

Figure 32: Diode Calibration Labview® Program Operation Panel

Since the calibration of the heater resistors cannot be taken directly as described in section A.1, the voltage and current must be analyzed. Figure 33 shows the user interface for the VI. The voltage array is displayed in 1d format along with a 2d format which represents the face of the module. When a heater is turned on and a data point is taken, the" I, V, T array" is populated. The voltage is taken at chip level with the 4-point probe technique mentioned earlier. This provides the actual voltage the heater is experiencing. The current was driven by the power supply which was calibrated by Draper Laboratory. The thermocouple average is also displayed so the heat sink temperature can be observed. Once all the data points are taken, the "heater cal slope" array is populated with the slope and the y intercept of each of the best-fit lines for the heaters. Once all this data is obtained, a graphical representation of all the heater slopes is plotted as can be seen on the right side of Figure 33. This enables rapid comparison

of resistance versus temperature of the heaters. The slope and intercept data along with the raw data is

saved in separate .txt files.

### Figure 33: Heater Calibration Labview® Program Operational Panel

The thermal resistance analysis program operates using the calibration data obtained from the heaters and the diodes. Instead of varying the temperature of the cooler, the power supplied to the module is varied resulting in the heating of the diodes. Each of the five different module types responds differently to the application of similar power levels. Figure 34 depicts the user interface for the VI. The resistance intensity plot and the temperature intensity plot are shown to facilitate quick reading of the surface temperatures. These intensity plots are graphical representations of the numerical arrays, which are also shown to the operator. Both these plots have a changeable range for graphing data points so

dead diodes, diodes that no longer respond linearly or predictably to temperature change, do not affect the representation of the data. Since there is loss in the thermal test stand board, the heater calibration data and the observed heater voltages are used to determine the actual power delivered to the module. The actual power dissipation in respect to heater location is shown in a numerical array along with its corresponding intensity graph. The average diode temp is also calculated so that outliers can be programmatically determined during the automatic operation of the program. Thermocouple readings are shown so that any inconsistencies in operation can be identified. Dead diodes are removed from the data before thermal resistance is calculated. The program has the option to alter the cooling method of the module so that it is compatible with fin heat sinks with and without fans. The arrays for "1D T\*", "1D Temperature heater orientation zeroed values" and the analysis of standard deviation are all used to eliminate diodes that are malfunctioning. The piece of data the program is designed to evaluate is the thermal resistance, which is shown at the top of the figure. This value is constantly being updated throughout the operation of the program, reflecting the real time thermal resistance of the module. In the calculation of the thermal resistance, the thickness of the TIM previously discussed is used. A safety shutoff is built in to the program to ensure the module doesn't overheat and damage the thermal testing stand.

Figure 34: Operation Panel of Labview Data Interpretation Program

### A.3 Fabrication of Stack

Due to the usage of high-density chip modules in a stacked fashion, a fabrication method to simulate such a stack was designed in order to determine the effect on the thermal properties of the module. This stack consists of two wafer pieces bonded together through the same means the bottom wafer is bonded to the interposer board. This way the thermal path between the two wafers mimics the path between the bottom wafer and the interposer. The top wafer is a purely mechanical component and therefore neither diode nor heater data is obtained from it. As shown in Figure 35, the presence of the wafer stack only slightly alters the thermal path described in the mathematical theory section.

### Figure 35: Thermal path for the stack of modules

A bare silicon wafer, populated with the TEA chips that had undergone similar processes to the other thermal wafer, was diced into 8x8 arrays of diodes. The diced wafer pieces were then bumped with 16mil SnPb solder balls with a reflow temperature of 183 °C. After this, some of the wafer pieces were set aside so that the adhesion layer for bonding between the wafer pieces could be created.